EUV光刻太贵,替代方案被考虑

01.半导体光刻技术的起源与发展

光刻是半导体工业的核心技术。自1960年仙童半导体的罗伯特·诺伊斯发明单片集成电路以来,光刻一直是主要的芯片制造技术。光刻技术本质上是,掩膜版用于对光刻胶进行图案化,从而实现图案化沉积和蚀刻工艺。光刻工艺的最终分辨率由所用光源的波长决定。在短波长光刻源的开发方面取得的进展,使得以摩尔定律为特征的电路密度不断增加。在过去光刻所需光源是Mercury discharged lamps,例如365nm时期采用的i-Line,但最近KrF为248nm或ArF为193nm的准分子激光器成为了首选光源。采用浸润式光刻技术,需要将透镜和芯片浸没在折射率比空气高的水中,由此ArF激光器获得的最终分辨率约为50nm。过去二十年,193nm波长的光刻技术得到了发展。虽然使用F2准分子激光的157nm光刻技术取得了一些突破,但人们主要关注的还是使用13.5nm软X射线作为光源的极紫外(EUV)光刻技术。荷兰光刻机龙头ASML在EUV技术的研发中发挥了主导作用,目前其EUV设备主要被包括英特尔、三星和台积电在内的先进CMOS代工厂用于生产。

02.实践中的光刻方法

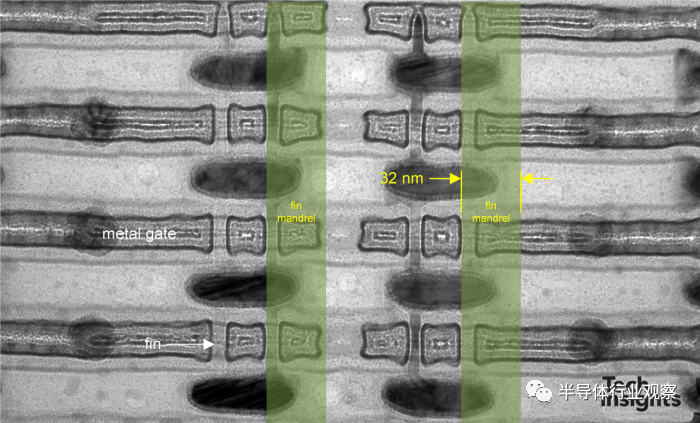

▲图2 三星 5LPE Gate和Fin Layout

自对准四重构图(SAQP)几乎可以肯定地用于对鳍片进行构图,鳍片心轴的大致位置如图所示,该心轴本应使用ArF 193nm浸没(ArF 193i)光刻法进行图案化,通过在心轴上形成侧壁间隔件,进而形成最终的鳍片图案。心轴的间距为108nm,然后将心轴移除,使用第一侧壁间隔物图案来创建第二组侧壁间隔件,最终给出27nm的鳍片间距。两组侧壁间隔物的大致位置和尺寸如图3所示,这是一张横截面TEM图像,显示了逻辑区域中三星5LPE工艺的27nm间距鳍片结构。

▲图3 三星 5LPE Fin Cross Sectio

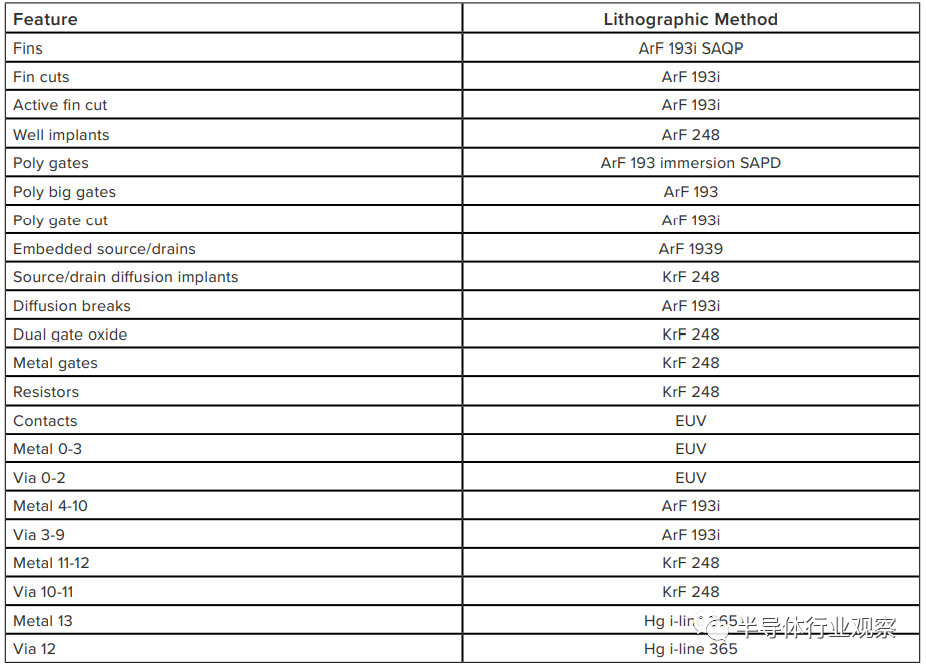

使用有源鳍片切割掩膜去除不需要的鳍片,并用浅沟槽隔离(STI)代替它们。图2所示的金属栅极很可能是使用自对准双图案化(SADP)技术形成的,其中心轴上的侧壁间隔物直接用于图案化多晶硅栅极,再用金属栅极取代。目前正在制造的先进半导体器件的尺寸明显小于用ArF浸没光刻法获得的约50nm最小半间距,这就需要开发越来越复杂的工艺技术。例如,根据最近TechInsights分析的结果,三星5nm LPE工艺使用了多种先进的光刻方法,包括EUV,如表1所示。

▲Table 1 Summary of photolithography methods applied in Samsung’s 5LPE process

SAQP光刻技术可以产生非常精细的间距特征,但仅限于创建单向定向的单轴结构,且线路末端需要特殊的切割掩膜,以防止相邻线路之间短路。EUV光刻没有这些限制,但成本更高。图4显示了三星5LPE设备CPU逻辑区中金属0布局的平面图TEM显微照片,观察到的最小金属间距约为44nm。此外,布局包括在两个正交方向上定向的线,如果使用SADP或SAQP ArF 193i光刻方法,通常不可能产生这种情况。▲图4 三星5LP Metal 0 Layout

03.纳米压印和直接自组装光刻

- 纳米压印光刻(NIL)

- 直接自组装(DSA)光刻

- 电子束光刻(EBL)

04.探索专利中的先进光刻技术创新

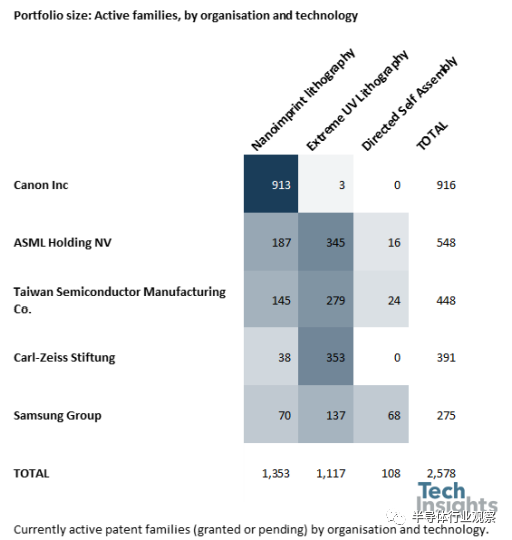

▲图5 Top 5 Companies by NIL, EUV and DSA Patent Holdings

这张图表展示了:- 佳能显然在NIL技术上下了很大****注

- ASML在EUV方面投入最多,但也积极参与NIL和DSA研究

- 从先进的光刻技术研发角度来看,台积电显然属于领先的代工厂。他们在EUV方面投资最多,但在NIL和DSA方面也很活跃

- 排名第五的三星也在对冲****注,尽管他们的专利活动水平远低于台积电

- 蔡司(Karl Zeiss)位列第四,毫不奇怪,作为光刻供应商,他们主要关注点是EUV

05.结语

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。