武汉新芯全新三维堆叠技术品牌 “3DLink”,锁定高速运算、存内计算、3D传感器ToF发力

武汉新芯研发多年的 3D IC 技术已崭露头角,更锁定高速运算、存内计算、3D 传感器 ToF 等热门领域进行卡位。日前,武汉新芯将三维堆叠技术注册成为全新品牌 “3DLink”,并在重庆登场的 ICCAD 2020 中重磅宣布细节。

武汉新芯从 2012 年开始布局 3D IC 技术,研发量产已步入第 8 年,键合良率高达 99.5%,拥有超过 400 个创新专利。

如今,3D IC 技术已经成为全球半导体大厂的新显学,包括台积电、三星都积极跨入。台积电今年宣布整合旗下堆叠到封装技术提出 “3DFabric” 新平台,身为 3D IC 技术领先厂商之一的武汉新芯也有新动作。

武汉新芯宣布,推出全新的三维堆叠技术品牌 —— 3DLink™,包括已进入量产的两片晶圆堆叠技术 S-stacking®、完成工艺研发的多片晶圆堆叠技术 M-stacking®,以及正在研发中的芯片 - 晶圆异质集成技术 Hi-stacking™。

武汉新芯代工业务处高级总监沈亮指出,过去三年,中国集成电路设计年会 ICCAD 已经成为武汉新芯宣布最新技术的舞台,公司每年都会在 ICCAD 年会上宣布三维堆叠技术的重大研发成果。

沈亮在 ICCAD 2020 “Foundry 与工艺技术” 专题论坛上,发表题为《XMC 3DLink™—— 面向高速运算和大容量存储芯片的解决方案》的演讲,激发许多芯片设计的创新思路。

当前有几个非常热门的应用场景,对于使用 3D IC 技术非常有兴趣,包括高速运算、存内计算、3D 传感器技术 ToF(Time-of-Flight)等。

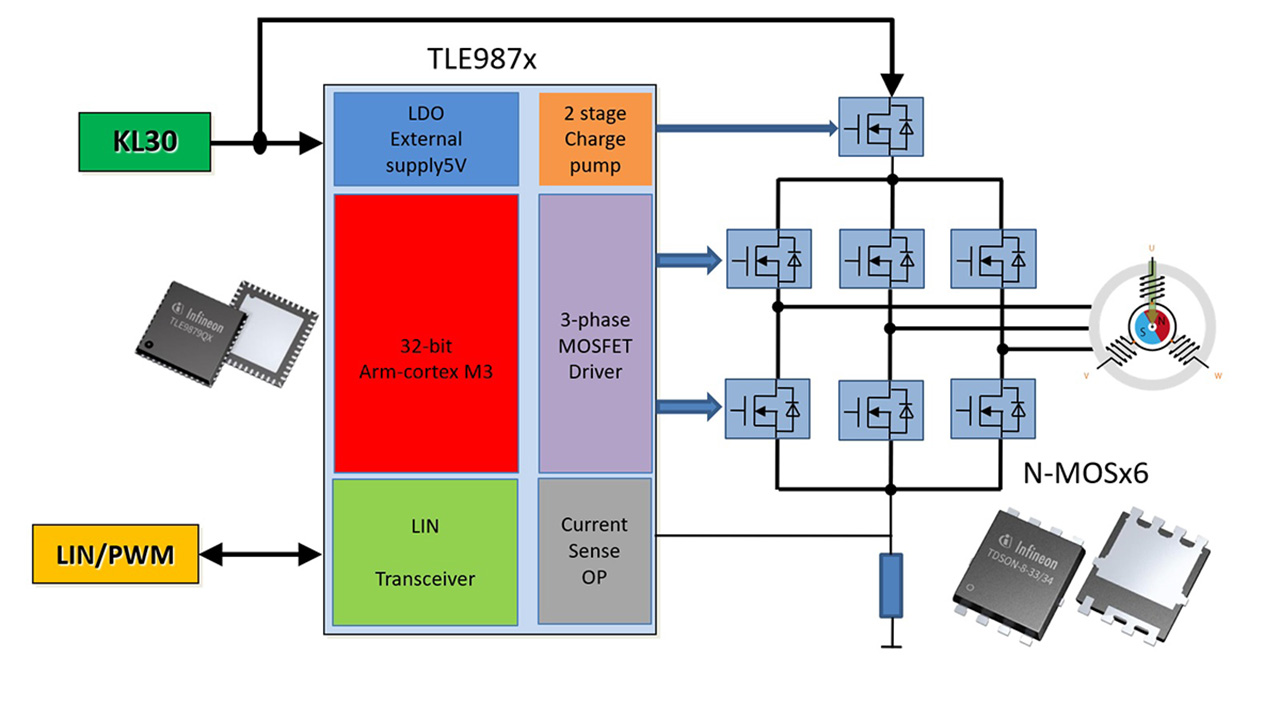

3D IC 技术将两片不同工艺的晶圆利用晶圆间的 Cu-Cu 直接互连,达到更高的互连密度及对准精度。通过直接互连实现了高带宽和高速运算。这项技术为高速运算芯片等提供创新的工艺和架构。善用 3D IC 技术优势更有助消费性电子装置在兼具高性能下,体积能更轻薄短小。

同样的产品,难道传统半导体工艺技术无法实现?

沈亮分析,高速运算终端和存内计算对带宽和算力有很高的要求,当然可以用先进制程工艺来实现,但代价是成本高,且不能确保未来持续供货的稳定性。而武汉新芯的晶圆堆叠技术 S-stacking® 可以在保持高性能优势下,解决这些问题。

在两个月前,武汉新芯的客户发布了一颗用于边缘计算的高速运算芯片。该芯片采用 S-stacking® 技术将 38nm 定制化 Memory 和 40nm SoC 结合后,迸发出 1840GB 的互联带宽,实现了 25TOPS 的运算量。而最近高通公司发布最新的骁龙 888 SoC,其中运用 5nm 工艺的 AI 处理核心运算能力是 26TOPS。也就是说我们用成熟工艺与先进架构的结合,成功追上了最顶级工艺产品的性能。目前以这颗高速运算芯片为主的系统已经能够通过简单的学习训练,离线自主识别出动物、植物,正在学习对人脸的判别。

3D IC 技术另一个优势领域是 “存算一体”,打破了冯・诺依曼架构,解决处理器和存储器分离造成的 “存储墙” 问题,缓解来回访存造成的延迟和高功耗。他分析,武汉新芯 S-stacking® 技术可直接将 Memory 和 Logic 晶圆堆叠在一起,并行高效处理架构,在不同功能的晶圆之间实现数据快速传输。

对于晶圆级 HBM,沈亮指出,多片晶圆堆叠技术 M-stacking® 打破传统封装级 HBM 的 Micro-bump 互连架构,采用无凸点(Bumpless)工艺来实现多晶圆直接键合,并利用混合键合工艺实现高密度互连。

还有一个领域也非常适合 3D IC 技术发力,就是主流的 3D 传感器 ToF。

自从苹果最近在 iPad 和 iPhone 12 搭载 dToF 镜头,3D 传感技术,特别是 dToF (direct Time-of-Flight) 成为全球最火热话题。

dToF 是一种主动式深度传感技术,直接通过测量光子传输时间差来计算与测量点距离,进而进行空间建模的技术。优点是探测距离远、扫描速度快且抗光干扰性佳,已应用在游戏机、AR/VR、智能汽车等领域。

该技术首先向被观测物体****一束脉冲激光,物体反射回的光子通过超高灵敏度的单光子雪崩二极管来触发信号。我们知道光速是每秒 30 万千米,那么在测量一个人的面部时,被鼻尖反射的光子和被人中反射的光子之间的时间差仅仅 0.000003 秒。因此,实时判别这样的时间差去计算距离,每一个触发信号点都需要一组单独的电路进行信号处理。而在空间建模的时候,更需要一个 QVGA 或者 VGA 的接收点矩阵。因此。即便是一个小的 QVGA 320x240 的矩阵,也需要巨大的连接带宽和处理速度,才能实时处理这些信号。这时候,武汉新芯的 3DLink™晶圆堆叠技术成为最好的解决方案。

沈亮指出, S-stacking® 技术可以通过将感光芯片和逻辑电路上下堆叠起来,满足 dToF 产品对数据处理带宽和速度的需求,兼顾了手机对低功耗和芯片小尺寸的需求。

从上面几个应用场景,可看出武汉新芯的三维堆叠技术平台的几个优势:创新架构、更高带宽、更低功耗和延时、更小芯片尺寸。目前武汉新芯的 3DLink™已经针对存储、高速运算芯片、传感器各自所要求的高带宽、低延迟和低功耗这些痛点,专门定制了三个针对性的工艺解决方案。

武汉新芯 3DLink™技术平台具备成熟的设计套件,支持定制化的开发,更是开放双臂希望与业界更多客户合作,让更多采用 3DLink™技术的高附加值技术解决方案能落地,共同打造创新的集成电路产品。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

手机电池相关文章:手机电池修复

pa相关文章:pa是什么