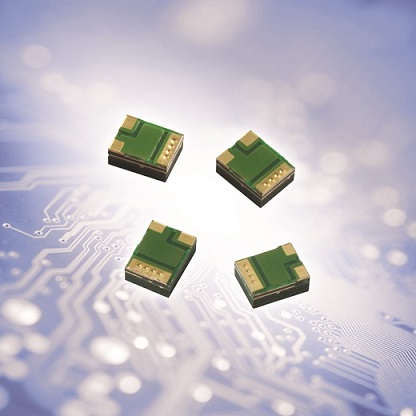

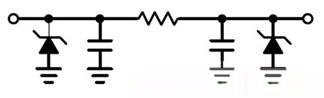

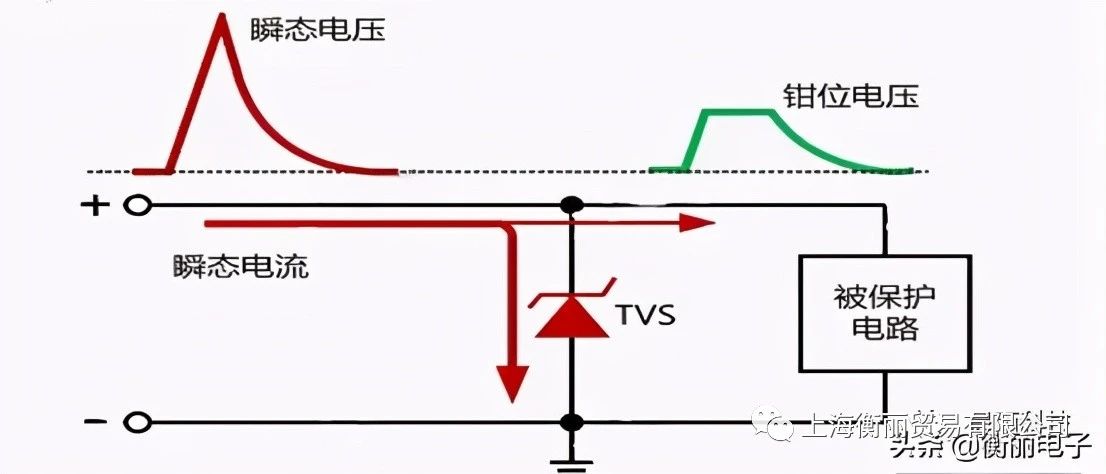

Littelfuse公司是全球电路保护领域的领先企业,日前宣布推出XGD系列XTREME-GUARD™ ESD抑制器,该系列产品提供0402规格和0603规格平顶贴片封装。 该系列产品基于突破性的ESD技术,可保护敏感电子设备免受不超过30kV静电放电的损坏,并且适合高达32VDC的高压应用。 如果与电路设计适当整合,XGD系列产品可安全吸收IEC61000-4-2国际标准所规定最高值近四倍的反复性ESD震击,同时不会造成性能减退。 极低电容让XGD系列适合用于高频和高速数据、视频、天线和

关键字:

Littelfuse ESD

过去50年的统计数据显示,商业航空旅行已经成为最安全、最可靠的交通方式之一。由于商业飞行的安全性不断提高,对先进的商用航空电子技术的需求也持续增长。2014年9月,Avascent预测全球商用航空电子设备市场将保持4.8%的增长速度,并将一直持续到2019年。该公司还预计2015年在固定翼商用飞机的商用航空电子系统上的花费将达到210亿美元。

Lucintel公司的分析师按照财务价值对商用航空电子设备最大的细分市场从大到小进行了排名:

1、通用网络和导航

2、控制系统

3、

关键字:

TVS二极管 ESD

汽车用电子系统的功能不断推陈出新,包括各种先进的驾驶辅助系统(ADAS),促使大量的通信接口协议陆续问世,为市场带来不同的通信速度、产品成本以及设计灵活性。意法半导体(STMicroelectronics,简称ST;纽约证券交易所代码:STM)推出两款整合优的异静电放电(ESD, Electrostatic Discharges)以及瞬变电压防护功能的控制器区域网络(CAN, Controller Area Network)总线,是市场上唯一符合所有主要汽车接口规范的接口保护芯片。

ESDC

关键字:

意法半导体 ESD

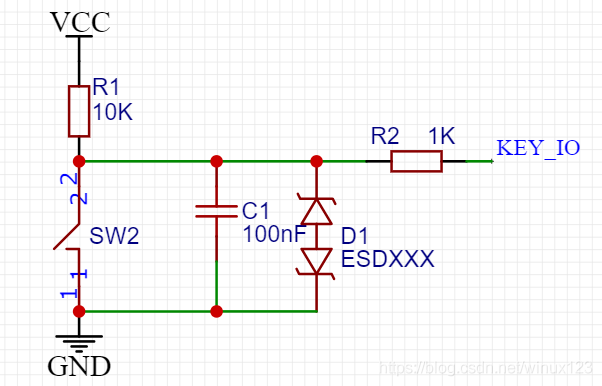

最近在做电子产品的ESD测试,从不同的产品的测试结果发现,这个ESD是一项很重要的测试:如果电路板设计的不好,当引入静电后,会引起产品的死机甚至是元器件的损坏。以前只注意到ESD会损坏元器件,没有想到,对于电子产品也要引起足够的重视。

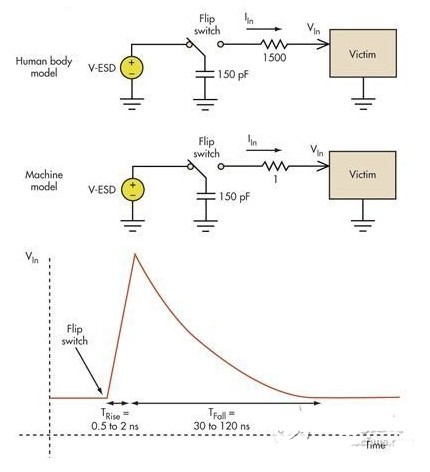

ESD,也就是我们常说的静电释放(Electro-Static discharge)。从学习过的知识中可以知道,静电是一种自然现象,通常通过接触、摩擦、电器间感应等方式产生,其特点是长时间积聚、高电压(可以产生几千伏甚至上万伏的静电)、低电量、小电流和作用时间短的

关键字:

PCB,ESD

汽车上的干扰源

汽车电系上的负载多种多样,既有小阻抗、大电流的阻性感性负载,也有小电流、高电压的脉冲发生装置,还有高频振荡信号源,它们不仅对外是潜在的干扰发射源,也是对车载电子产品的干扰源。另外,由于高机动性,汽车也可能会处于各种可以想像得到的从低频到高频的复杂电磁场中,由此产生的电磁干扰耦合也会影响汽车电子电气系统的正常运行。汽车电系内的电压可以归纳为以下几类:正常工作电压、异常稳态电压、无线电干扰电压、瞬变过电压和静电放电。

汽车电器的电磁兼容设计

汽车电器的电磁兼容环境应是一个

关键字:

电磁兼容 ESD

在PCB板的设计当中,可以通过分层、恰当的布局布线和安装实现PCB的抗ESD设计。通过调整PCB布局布线,能够很好地防范ESD.尽可能使用多层PCB,相对于双面PCB而言,地平面和电源平面,以及排列紧密的信号线-地线间距能够减小共模阻抗和感性耦合,使之达到双面PCB的1/10到1/100.对于顶层和底层表面都有元器件、具有很短连接线。

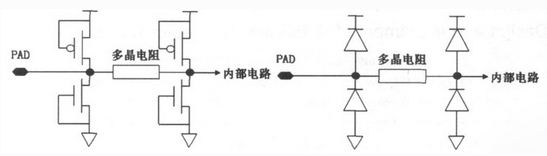

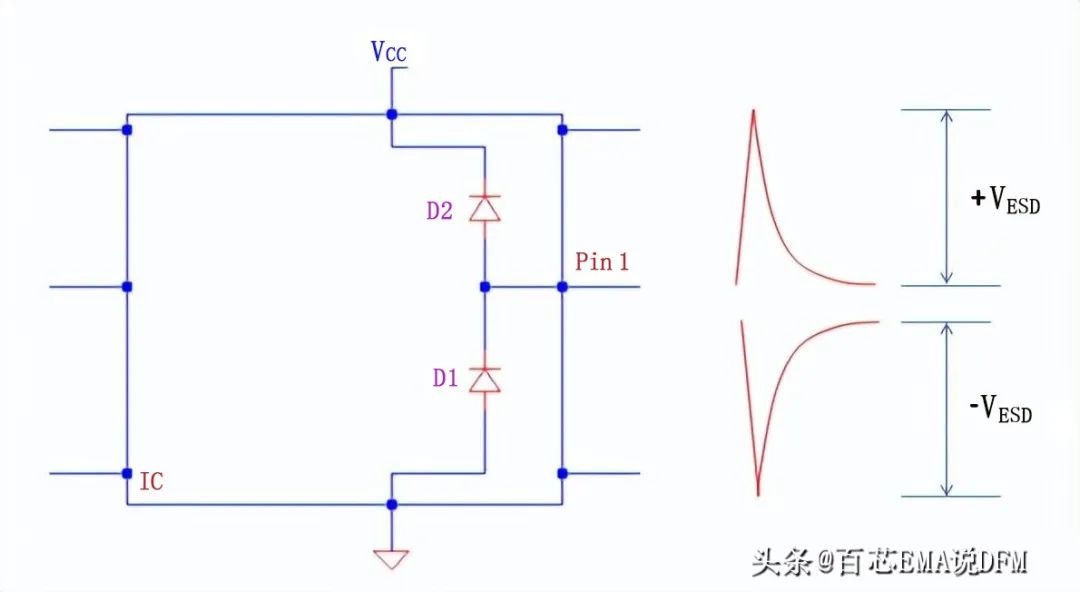

来自人体、环境甚至电子设备内部的静电对于精密的半导体芯片会造成各种损伤,例如穿透元器件内部薄的绝缘层;损毁MOSFET和CMOS元器件的栅极;CMOS器件中的触发

关键字:

PCB ESD

最近在做电子产品的ESD测试,从不同的产品的测试结果发现,这个ESD是一项很重要的测试:如果电路板设计的不好,当引入静电后,会引起产品的死机甚至是元器件的损坏。以前只注意到ESD会损坏元器件,没有想到,对于电子产品也要引起足够的重视。

ESD,也就是我们常说的静电释放(Electro-Static discharge)。从学习过的知识中可以知道,静电是一种自然现象,通常通过接触、摩擦、电器间感应等方式产生,其特点是长时间积聚、高电压(可以产生几千伏甚至上万伏的静电)、低电量、小电流和作用时间

关键字:

PCB ESD

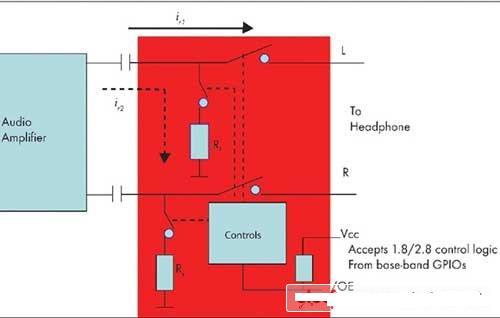

随着市场对功能丰富的手机需求越来越强劲,具有特殊应用性能的模拟开关得到了最终设计的持续青睐。此举不仅能降低材料成本(BOM),还有助于提升设计性能并满足对产品上市时间的要求。本文将通过若干实际用例指导系统设计人员如何降低冲击噪声(pop noise)、检测充电器及改进眼图张度。

同时,本文还通过比较传统方案与集成方案说明了手机市场向多媒体设计发展过程中采用这种高性能模拟产品所带来的好处。

降低冲击噪声

由浪涌电流引发的冲击噪声仍是设计人员所面临的艰巨挑战,特别是当最终用户启动音乐和通

关键字:

模拟开关 ESD

目前对于许多流行的手机(尤其是翻盖型手机)而言,手机的彩色LCD、OLED显示屏或相机模块CMOS传感器等部件,都是通过柔性电路或长走线PCB与基带控制器相连的,这些连接线会受到由天线辐射出的寄生GSM/CDMA频率的干扰。同时,由于高分辨率CMOS传感器和TFT模块的引入,数字信号要在更高的频率上工作,这些连接线会像天线一样产生EMI干扰或可能造成ESD危险事件。

上述这种EMI及ESD干扰均会破坏视频信号的完整性,甚至损坏基带控制器电路。受紧凑设计趋势的推动,考虑到电路板空间、手机工作频率上

关键字:

EMI ESD

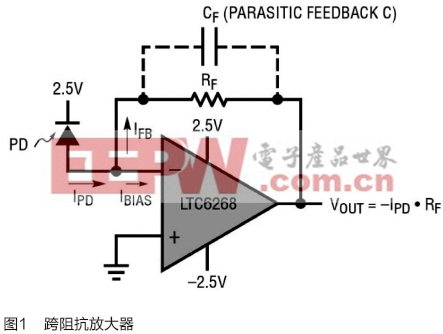

光电二极管广泛见诸于众多的应用,其用于把光转换为可在电子电路中使用的电流或电压。从太阳能电池到光数据网络、从高精度仪器到色层分析再到医疗成像等均在此类应用之列。所有这些应用都需要用于对光电二极管输出进行缓冲和调节的电路。对于那些需要高速和高动态范围的应用,通常采用如图 1 所示的跨阻抗放大器 (TIA) 电路。在图1中,反馈电容显示为一个寄生电容。对于许多应用来说,这是一个为确保稳定性而有意布设的电容器。

该电路让光电二极管处于“光电导模式”,并在其负极上施加了一个偏

关键字:

光电二极管 放大器 LTC6268 电容器 ESD 201504

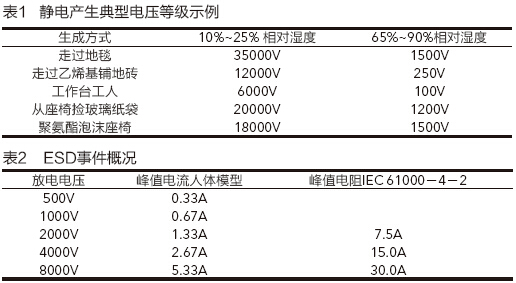

我们的手都曾有过静电放电(ESD)的体验,即使只是从地毯上走过然后触摸某些金属部件也会在瞬间释放积累起来的静电。我们许多人都曾抱怨在实验室中使用导电毯、ESD静电腕带和其它要求来满足工业ESD标准。我们中也有不少人曾经因为粗心大意使用未受保护的电路而损毁昂贵的电子元件。

对某些人来说ESD是一种挑战,因为需要在处理和组装未受保护的电子元件时不能造成任何损坏。这是一种电路设计挑战,因为需要保证系统承受住ESD的冲击,之后仍能正常工作,更好的情况是经过ESD事件后不发生用户可觉察的故障。

与人

关键字:

ESD

ESD(静电放电)是CMOS电路中最为严重的失效机理之一,严重的会造成电路自我烧毁。论述了CMOS集成电路ESD保护的必要性,研究了在CMOS电路中ESD保护结构的设计原理,分析了该结构对版图的相关要求,重点讨论了在I/O电路中ESD保护结构的设计要求。

1 引言

静电放电会给电子器件带来破坏性的后果,它是造成集成电路失效的主要原因之一。随着集成电路工艺不断发展,CMOS电路的特征尺寸不断缩小,管子的栅氧 厚度越来越薄,芯片的面积规模越来越大,MOS管能承受的电流和电压也越来越小,而外围的

关键字:

ESD CMOS

显示器通常也被称为监视器。显示器是属于电脑的I/O设备,即输入输出设备。它可以分为CRT、LCD等多种。它是一种将一定的电子文件通过特定的传输设备显示到屏幕上再反射到人眼的显示工具。本文为大家介绍电子显示屏、等离子显示屏、液晶显示屏及硅基液晶显示屏的经典应用案例,供大家参考。

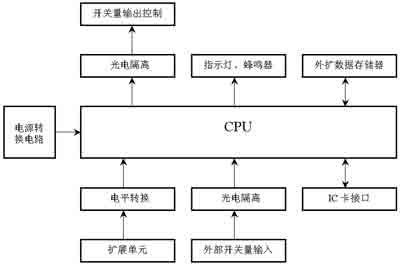

蓝牙无线显示屏系统的设计方案

本文介绍一种蓝牙无线显示屏系统的设计方案。使用蓝牙技术可以短距离无线控制显示终端,实现图像和字符数据的无线传输和显示,免去了有线连接所带来的缺陷,可以应用在多种领域。

基于触摸显示

关键字:

EMI ESD

TE Connectivity旗下业务部门TE电路保护部现在提供全新PolyZen YC器件系列,这些器件提供了一种集成式方法帮助保护平板电脑、机顶盒、硬盘和DC电源端口等消费电子产品,避免静电放电(ESD)和其它可能危害应用并且导致安全和保修问题之电气过压事件引起的损坏。全新PolyZen ZEN056V230A16YC和ZEN056V260A16YC器件在紧凑的(4.0mm x 5.0mm x 1.2mm)封装中结合了一个精密齐纳二极管和可自恢复PolySwitch聚合物正温度系数(PPTC)器件

关键字:

TE Connectivity PolyZen ESD

摘要:本文通过采用合适的过电流和过电压保护元件,生产商可保证其产品成为用户生活不可或缺的一部分。选择正确的保护元件也保证了各应用产品符合安全和功能因素相关的规章条例的要求。

许多用户都没有意识到他们自己每天在使用的电子设备存在着最大的风险。电路保护是所有电子设备必有的特性——不论是车载、家用或是工用电子设备——因为只要人体接触含敏感电子半导体的器件,就会出现ESD(静电放电)现象。

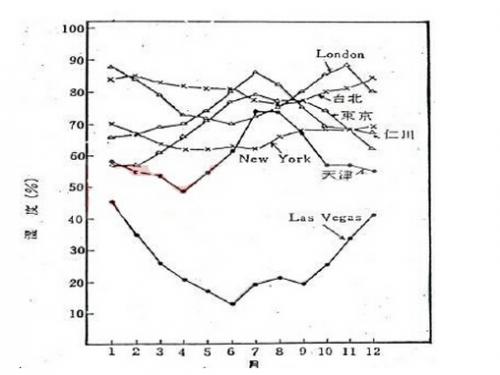

如果周围的空气特别干燥,比如天气正好非常炎热或非常寒冷,刚把

关键字:

电路保护 ESD TVS 集成电路 HBM 201411

esd介绍

ESD的意思是“静电释放”的意思,它是英文:Electro-Static discharge 的缩写

ESD知识介绍

静电是一种客观的自然现象,产生的方式多种,如接触、摩擦等。静电的特点是高电压、低电量、小电流和作用时间短的特点。

人体自身的动作或与其他物体的接触,分离,摩擦或感应等因素,可以产生几千伏甚至上万伏的静电。

静电在多个领域造成严重危害。摩擦起电和人体静电是电子工业中的两 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473