Altera公司 (NASDAQ: ALTR)今天宣布发布Quartus® II软件13.1版,通过大幅度优化算法以及增强并行处理,与前一版本相比,编译时间平均缩短了30%,最大达到70%,进一步扩展了在软件效能方面的业界领先优势。软件还包括最新的快速重新编译特性,适用于客户对Altera Stratix® V FPGA设计进行少量源代码改动的情形。采用快速重新编译特性,客户可以重新使用以前的编译结果,从而保持性能,不需要前端设计划分,进一步将编译时间缩短了50%。

关键字:

Altera Quartus FPGA DSP

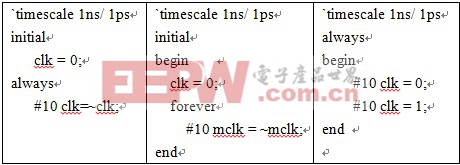

Testbench,就是测试平台的意思,具体概念就多不介绍了,相信略懂FPGA的人都知道,编写Testbench的主要目的是为了对使用硬件描述语言(HDL)设计的电路进行仿真验证,测试设计电路的功能、部分性能是否与预期的目标相符。

关键字:

FPGA Quartus Testbench 开发板 异步复位

很多人都说QUARYUSII中的IP核是收费的,不可以直接用的,其实不然,下面我以FIR滤波器的核的使用来给大家介绍IP核 ...

关键字:

QUARTUS II IP核 调用方法

Altera公司 (Nasdaq: ALTR) 日前宣布,推出Quartus® II软件12.1版——在CPLD、FPGA、SoC FPGA和HardCopy® ASIC设计方面,性能和效能在业界首屈一指的设计套装软件。这一最新版软件进一步简化传统的硬件开发任务,增强了Quartus II软件的高级设计环境,因此,用户提高了效能,同时全面受益于Altera器件的各种前沿功能。

关键字:

Altera Quartus FPGA DSP

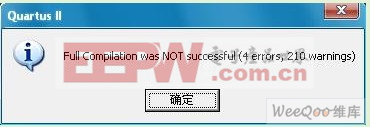

关于quartus生成IP核的仿真出错问题的解决,对MegaCore的生成从头至尾操作了一遍,说实话很是复杂,不过,大家都知道quartus的IP可以直接拿来用的,大大节省了开发时间,而且其代码是绝对优化的;所有的前奏都操作成功,设置没什么问题,开始对生成的fft.vhd文件

关键字:

出错 问题 解决 仿真 IP quartus 生成 关于

Altera公司(Nasdaq: ALTR)日前发布业界成熟可靠的最新版Quartus® II开发软件——对于FPGA设计,性能和效能在业界首屈一指的软件。Quartus II软件12.0版进一步提高了用户的效能和性能优势,例如,对于高性能28-nm设计,编译时间缩短了4倍。其他更新包括扩展28-nm器件支持,初次支持Altera SoC FPGA,增强Qsys系统集成和DSP Builder工具,以及经过改进的知识产权(IP)内核等。

关键字:

Altera FPGA Quartus

quartus的IP仿真错误分析, 大家都知道quartus的IP可以直接拿来用的,大大节省了开发时间,而且其代码是绝对优化的;所有的前奏都操作成功,设置没什么问题,开始对生成的fft.vhd文件进行编译,点击Start Compilation,第一感觉:慢!编译很

关键字:

分析 错误 仿真 IP quartus

Tsu/Tco 在Quartus II 的报告中有两种不同含义. 1. 片内的Tsu/Tco 是指前级触发器的Tco 和后级触发器的Tsu, 一般来说都是几百ps 级别的. 可以通过“List Paths”命令查看。这里的Tsu/Tco 主要由器件工艺

关键字:

Quartus Tsu Tco II

Altera公司今天宣布推出Quartus II软件11.1版——在CPLD、FPGA和HardCopy ASIC设计方面,业界性能和效能最好的软件。这一新版软件扩展了Altera 28-nm FPGA支持,包括对Arria V和Cyclone V FPGA的编译支持,还增强了对Stratix V FPGA的支持。Quartus II 软件11.1版增加了支持Altera系统级调试工具——系统控制台。系统控制台提高了调试的抽象级,能够与Altera SignalTap™ II嵌入式逻辑分析器等底层调试工

关键字:

Altera Quartus II

摘要:针对目前在嵌入式平台中使用SD卡控制器专用芯片价格昂贵、软件模拟SPI时序控制读写速度较慢的问题...

关键字:

控制器 IP核 Quartus II

近年来,随着集成电路技术的迅猛发展,特别是可编程逻辑器件的高速发展,EDA(ElectronicDesignAutomatio...

关键字:

EDA FPGA VHDL Quartus

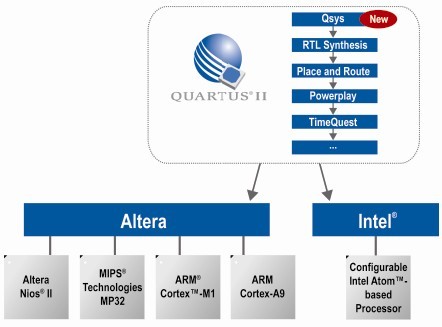

为加速实现嵌入式系统中可编程逻辑与处理器的集成,Altera公司今天发布其嵌入式计划。通过这一计划,Altera为设计人员提供了基于Quartus® II开发软件的单一FPGA设计流程——包括新的Qsys系统级集成工具、公用FPGA知识产权(IP)库,以及新的ARM® Cortex™-A9 MPCore™和MIPS®技术公司MIPS32嵌入式处理器产品等。利用这一设计流程,嵌入式设计人员能够迅速方便的面向Altera Nios&r

关键字:

Altera 嵌入式 Quartus

quartus的IP仿真出错解决方案,大家都知道quartus的IP可以直接拿来用的,大大节省了开发时间,而且其代码是绝对优化的;所有的前奏都操作成功,设置没什么问题,开始对生成的fft.vhd文件进行编译,点击Start Compilation,第一感觉:慢!编译很慢,

关键字:

解决方案 出错 仿真 IP quartus

ModelSim+Synplify+Quartus的Altera FPGA的仿真实现,工作内容:

关键字:

仿真 实现 FPGA Altera Synplify Quartus ModelSim

--quartus介绍

您好,目前还没有人创建词条--quartus!

欢迎您创建该词条,阐述对--quartus的理解,并与今后在此搜索--quartus的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473