DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计(08-100)

DDR2 SDRAM接口的信号线分为4组,以下以MPC8548命名方式为准,命名和DDR2 SDRAM芯片资料的区别在于信号名之前多一个字母”M”【7】:

本文引用地址:http://www.eepw.com.cn/article/91686.htm1) 数据组:MDQS/MDQS#[8:0], MDM[8:0], MDQ[63:0], MECC[7:0]

2) 地址组:MBA[2:0], MA[15:0], MRAS#, MCAS#, MWE#

3) 命令组:MCS#[3:0], MCKE[3:0], MODT[3:0]

4) 时钟组:MCK/MCK#[5:0]

PCB设计时,建议布线顺序依次为:数据组,地址组,控制组,时钟组,电源。

对于单端信号线,阻抗控制在50~60欧姆内。对于差分信号线,阻抗控制在100~120欧姆内。

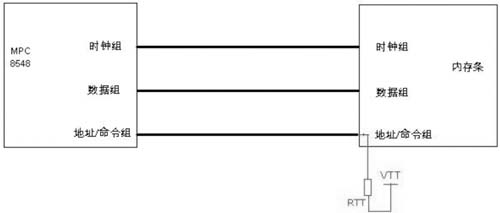

如果使能了ODT功能,数据组无需外部匹配电阻,走线直接从MPC8548连接到内存条即可。而地址组和命令组需要在内存条末端利用外部电阻RTT上拉到VTT电平实现匹配,电阻值需要经过仿真确定。如图6,考虑到最佳的信号完整性,RTT应该放在内存条之后,即地址/命令组信号走线从MPC8548出来,应该先到内存条的引脚,然后再走到RTT电源平面实现终端匹配。对于时钟组,一般而言,内存条上都包含了100~120欧姆的差分终端电阻,所以在PCB上无需外加匹配。

图6 MPC8548和DDR2 SDRAM内存条硬件接口设计

由于本设计采用8位的DDR2 SDRAM芯片,因此,对数据组可以分为9个小组:MDQS/MDQS#[0],MDQ[7:0],MDM0为第一组;MDQS/MDQS#[1], MDQ[15:8],MDM1为第二组;依次类推;MDQS/MDQS#[8],MECC[7:0],MDM8为第九组。对这九小组数据线,要求各小组之内,走线在同一层并拥有相同数目的过孔,走线长度差异控制在20mil之内,所有的信号线走线必须以完整的地层作为参考。不同小组之间,走线长度差异控制在500mil之内。对每一小组,小组内的8根MDQS信号线的线序可以根据走线方便的目的进行调整。需要注意,在本设计中,采用的内存条上的存储芯片是8位的(即内存条上每片DDR SDRAM芯片有8根DQ数据线),因此每8位MDQ信号归为一个小组,市场上还有许多4位,16位的内存条,如果需要兼容这些内存条,硬件设计中需要注意应该以每4位MDQ信号归为一个小组。数据组的信号线和其他组的信号线间距要求在25mil以上,数据组内信号线间距要求在10mil以上。对于差分的MDQS和MDQS#信号,走线长度差异应该控制在10mil之内。

对地址/命令组,该组内信号线长度差异应控制在100mil之内。走线以1.8V电源平面或完整的地层作为参考层。走线和其他组的信号线间距保证在25mil以上。该组内信号线间距保证在10mil以上。

对时钟组,差分信号对内走线长度差异控制在10mil内,尽量在同一层内走线,如果需要换层,两根差分信号应该一起换层。与其他组的信号间距在25mil以上。在MPC8548一侧,一共提供了6对相位相同的时钟对,即MCK/MCK#[5:0],其目的是为了兼容内存条设计和分立的内存芯片设计。例如在本设计中,如果选用分立的8位存储芯片,一共需要9片,如果MPC8548只提供一对时钟对,其驱动能力显然无以满足9片存储芯片,因此需要由MPC8548提供更多的时钟对输出。如果选用内存条,需要根据内存条的不同种类来决定需要使用多少对时钟对。根据对MCK/MCK#信号是否提供驱动,内存条可以分为Buffered DIMM(缓冲驱动式内存条)和Unbuffered DIMM (非缓冲驱动式内存条),对于前者而言,由于MCK/MCK#在内存条上需要经过缓冲再送到DDR2 SDRAM芯片,即在内存条上利用缓冲器(通常是带锁相环的缓冲器)保证了该信号的驱动能力,所以只需要MPC8548提供一对时钟对(例如MCK/ MCK#[0])送到内存条即可。对于后者而言,内存条上不提供对时钟对的驱动,通过计算可以知道从MPC8548提供的每对时钟对,能可靠驱动3个DDR2 SDRAM芯片作为负载。因此需要使用MPC8548输出的3对时钟对以驱动内存条上的9片DDR2 SDRAM芯片。对于没有使用到的时钟对,可以通过配置MPC8548的内部寄存器DDRCLKDR进行关闭。

在电源设计方面,需要仔细计算VTT电源发生器及其电源平面是否能满足设计所需要的功耗;需要仔细对VTT, VDDQ, VREF进行去耦滤波;VTT电源平面应该和内存条紧紧相邻;VREF走线宽度建议为20~25mil并和同层的其他电源或信号有至少20mil的间距,VREF必须能跟随VDDQ的变化,建议VREF通过电阻分压网络从VDDQ直接得到,分压电阻精度要求为1%;

设计时,还需要仔细考虑信号时序的要求。数据组信号的时序需要参考本小组的MDQS/MDQS#信号,并利用这对差分对的交叉点采样;地址和命令组信号的时序需要参考对应的时钟组信号,并利用其上升沿采样。对于DDR2 SDRAM,建立时间和保持时间需要考虑由于信号边沿不单调造成的时序降额,计算公式如下:

tSETUP = tSETUP(base) + tSETUP(derating)

tHOLD = tHOLD(base) + tHOLD(derating)

其中,tSETUP和tHOLD是总的建立时间和保持时间要求;tSETUP(base)和tHOLD(base)是从芯片文档能直接得到的建立时间和保持时间的基本要求;tSETUP(derating)和tHOLD(derating)是根据信号及其参考时钟的真实爬升速率查表得出的降额值,该表格可以从芯片文档得到。

这种查表计算降额值的方法,将造成很大的工作量。在实际设计中,一般是利用Hyperlynx等仿真软件直接得到降额值,从而确定信号的时序裕量。特别需要注意的是地址组,由于地址组信号的负载数目一般都比相应的时钟信号多,因此需考虑负载对时序造成的影响。

结语

存储芯片在电子产品中扮演着重要的角色,其性能的高低直接决定着产品的性能。相比DDR SDRAM,DDR2 SDRAM在多方面进行了技术提升,其必将在电子产品市场中发挥越来越重要的作用。

上拉电阻相关文章:上拉电阻原理

评论