DDR2 SDRAM介绍及其基于MPC8548 CPU的硬件设计(08-100)

* 4n数据预取

本文引用地址:http://www.eepw.com.cn/article/91686.htmDDR SDRAM的数据预取能力是2,即芯片内部能以2倍于时钟运行的速度预取数据,从而使得芯片内核工作频率仅需要为外部数据传输率的一半。DDR2 SDRAM的数据预取能力是4,即芯片内核工作频率仅需要为外部数据传输率的1/4。而对于SDRAM,芯片内核工作频率等于外部数据传输速率。所以在同样的内核频率下,DDR SDRAM的数据传输速率比SDRAM高一倍,而DDR2 SDRAM的数据传输率比DDR SDRAM又高一倍。

例如,DDR2和DDR1 SDRAM的外部数据传输率都为400Mb/s的情况下,对于DDR2 SDRAM而言,其内核工作频率仅需要为100MHz,而对于DDR SDRAM,其内核工作频率需要为200MHz,如果是SDRAM,则其内核频率要求为400MHz,正是因为如此高的内核频率无法在技术上实现,因而SDRAM的数据传输率无法达到400Mb/s。

利用这项技术,DDR2 SDRAM可以在不提高内核工作频率的前提下(即无需对芯片做大的技术革新),大大提高外部数据传输速率,从而获得更高的性能。值得提及的是,目前正在研发的DDR3 SDRAM技术,其数据传输率比DDR2 SDRAM又有大幅度提高,其并不是源于技术上的巨大变革,而是因为采用了8n数据预取技术。

根据数据传输速率的不同,DDR SDRAM有如下系列:266Mb/s,333Mb/s, 400Mb/s,而DDR2 SDRAM有如下系列:400Mb/s,533Mb/s, 667Mb/s,800Mb/s, 1066Mb/s。可以看出,DDR2 SDRAM直接从DDR SDRAM的最高的数据传输率起步,最高可以达到1066Mb/s以上,该性能的大幅提升,正是利用了这种4倍数据预取技术。

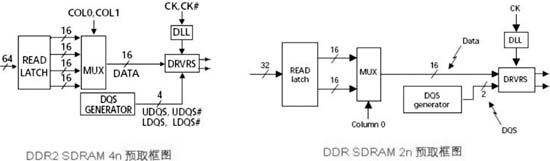

图5提供了DDR SDRAM和DDR2 SDRAM的数据预取框图以便比较。

图5 16位存储芯片的数据预取框图

* 差分DQS/DQS#信号

DDR SDRAM采用单端DQS信号。

如前文所述,目前广泛应用的DDR2 SDRAM,数据传输率最高已经达到1066Mbit/s,即DQS和DQ的变化率都将达到一秒钟1066M次,其中,DQS作为数据信号DQ的采样参考源,如果采用单端信号已经不足以保证其在高速变化时的信号完整性。

上拉电阻相关文章:上拉电阻原理

评论