eASIC推出新一代45nm结构化ASIC

半导体调研机构Gartner多年来一直在跟踪ASIC设计项目数量,其趋势已经无疑被认定向下。最新技术的ASIC设计费用已经上升到一个很高点,以致许多中小规模的公司用不起而只能采用FPGA。而ASIC只有依靠正在研发的各种降低其设计费用的新方法才有希望挽回颓势。

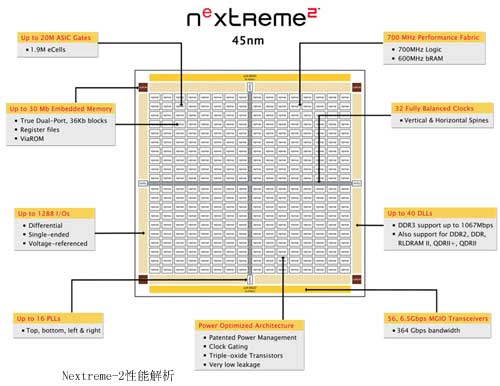

本文引用地址:http://www.eepw.com.cn/article/87842.htm拥有独特的过孔层布线定制专利技术以及零掩模费和无最低订货量限制的新结构化ASIC平台供应商eASIC在其90nm Nextreme ASIC产品的基础上,又发布了其新一代Nextreme-2系列产品。Nextreme-2系列是目前市面上唯一的 45nm 无掩模费用ASIC,其规模多达2千万门。

eASIC资深市场总监Jasbinder Bhoot对EDN China表示,Nextreme-2并不是传统意义上的结构化ASIC(表一),而是一个全新的ASIC平台。Nextreme-2系列采用特许Chartered半导体的45nm低功耗(LP)工艺生产制造,拥有业界效率最高的查找表(LUT)结构。 其逻辑组织架构能够提供高达700 MHz的性能(前一代为300 MHz),不需要乘法器就能实现2.4 TeraMACs DSP信号处理能力。

与最新工艺的FPGA相比,由于结合了三重氧化物晶体管、45nm 低功耗工艺和 eASIC 专利的功率管理结构,Nextreme-2的功耗可以降低80%。 低功耗的优点使得 Nextreme-2 成为追求功耗效率的应用场合的理想选择,以达到减小系统成本、满足严格耗电指标的要求。

Nextreme-2系列还包含多达56条 MGIO (多G比特输入输出口)。每条IO都能工作在6.5Gbps,总计提供364Gbps带宽。在高性能网络应用中,如交换机、路由器、流量管理、城域网传输设备和移动回程设备,由于具备 MGIO(多G比特输入输出口),Nextreme-2 将成为FPGAs和ASICs之外唯一的选择。

Bhoot并不同意“使用逻辑验证和仿真以及FPGA原型设计是降低结构化ASIC功能性逻辑错误设计问题风险的有效方法”这一说法,因为eASIC的价值就在于零掩膜、短周期和易使用。“我们有使用FPGA开发原型的客户,但也有直接使用eASIC产品的客户,因为产品开发周期短,并且不用做两次板级验证,如果客户要开发某系统芯片,在ASSP、结构化ASIC和FPGA之间如何选择?答案是注意几个方面:产品研发周期、处理器和ISA allegiance、在硬件和软件中的差异化需求、操作系统的可用性、性价比。”

eASIC认为Nextreme-2的推出标志着一个ASIC新纪元才刚刚开始,并正在逆转衰退的ASIC设计趋势。Bhoot强调,不同于FPGA复杂的设计工具,eASIC为该系列产品提供简单的设计工具(Magma Blast Create SA)和设计流程,秉承eASIC 做得起定制芯片的原则,Nextreme-2采用最新的45nm技术设计定制芯片,客户只需6周即可流片,而且没有最小定货量的要求。Bhoot相信,由于没有最小定量要求,Nextreme-2 ASIC系列为加速eASIC的市场扩张,进入半导体工业最大的市场——850亿美元的全球逻辑市场铺平了道路。

据悉,目前eASIC正与富士通等早期客户合作,计划批量应用将在2008年第四季度开始。

评论