基于Verilog-HDL的轴承振动噪声电压峰值检测

引言

本文引用地址:https://www.eepw.com.cn/article/83375.htm在轴承生产行业中,轴承振动噪声的峰值检测是一项重要的指标。以往,该检测都是采用传统的模拟电路方法,很难做到1:1地捕捉和保持较窄的随机波形的最大正峰值。本文叙述了基于Verilog-HDL与高速A/D转换器相结合所实现的快速轴承噪声检测方法。

1.1 轴承振动噪声的产生及检测

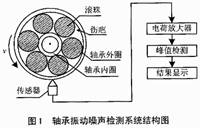

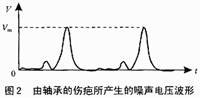

图1是轴承振动噪声电压峰值检测系统的示意图。由于加工设备、技术、环境等因素的影响,生产的轴承都程度不同地带有伤疤。图1中,假设某待测轴承有一处伤疤。由于伤痕的存在,轴承在转动过程中,伤疤将与滚珠产生摩擦,从而表现在轴承整个产生微小的振动。这一振动通过加速度传感器输出电压信号,经电荷放大器、峰值检测后,即后得到振动噪声的峰值电压。图2给出了在有伤疤情况下的传感器输出电压波形。

1.2 模拟式的峰值电压保持电路

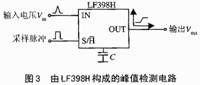

以往的轴承振动噪声峰值电压检测,均采用了模拟式的峰值电压检测法。图3示出了由采样保持电路LF398H构成的该类检测电路。当噪声电压到来后,采样信号跟随模拟信号电压到峰值处,之后采样脉冲消失,电路处于保持状态。保持电容C上即存储了模拟信号的峰值电压Vm。要想较快地跟随输入电压Vin的变化,保持电容C的容量就应相对减小;而C的相对减小,又会导致在保持电压期间,输出电压Vout的下降速率加快。这两者相互矛盾,从而使这种电路难以达到较高的性能。

1.3 数字式的峰值电压检测

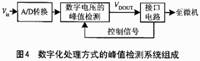

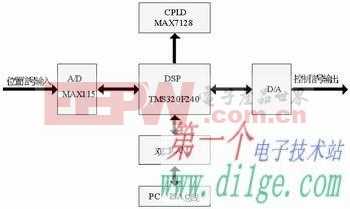

模拟式的峰值检测电路不易做到高速采样。采桥保持电路经长期使用后,多方面的性能会发生明显变化,且不易批量化生产;而由数字电路组成的系统可以做到结构简单、调试方便,长期使用不会导致系统性能指标的下降。图4是一种数字式的峰值检测系统的组成方案。它由A/D转换部分和数字电压的峰值检测部分组成,接口电路内含微处理器,负责与微机进行数据通信和接收来自微机的控制信号,并控制检测系统的工作。根据应用对象的不同,A/D转换器的采样速率可高达上百Msps[1],并可自带采样保持电路。与A/D转换器相接的数字电压峰值检测电路可采用FPGA,其工作速度也中达上百Msps。因此,在信号的处理速度方面两者都是优于传统的模拟电路方式的。

2 基于Verilog-HDL的峰值电压检测方案

2.1 逻辑功能的设计

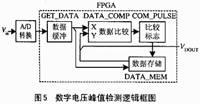

图5给出了数字电压峰值检测框图。图中除了A/D转换器外,虚线部分所示均为FPGA组成的功能模块。其功能由Verilog-HDL(HDL:硬件描述语言)来实现[2]。工作原理如下:由A/D转换器取得的数字电压送入数据缓冲模块GET_DATA,GET_DATA中的数据与来自数据存储模块DATA_MEM中的数据都送入数据比较模块DATA_COMP进行比较。如果X端的数据大于Y端的数据,比较标志模块产生标志信号,同时该信号将X端的数据打入数据存储模块DATA_MEM中(系统复位后,DATA_MEM中的数据为最小值0),进而实现了保持2个数据中较大的一个功能。当振动噪声电压经A/D转换器转换成数字电压后,数据存储模块便依A/D转换的次数做相应次的比较,最终将噪声电压的峰并保持下来。VDOUT为数字式的峰值输出电压。

评论