逻辑分析仪在嵌入式系统调试中的应用

引言

本文引用地址:https://www.eepw.com.cn/article/80381.htm如今,嵌入式系统的功能越来越强,但设计和验证问题也变得越来越复杂。善用逻辑分析仪,可以提高查找和解决问题的效率,尤其是最困扰嵌入式系统工程师的时序问题和一些硬件本身固有的问题。

逻辑分析仪介绍

逻辑分析仪(Logic Analyzer)是一种数字数据域测试的常用仪器,它可以把测试通道上的逻辑信号捕捉并存储下来,供设计人员分析。与示波器相比,逻辑分析仪具有测量通道数多(一般有32个通道);触发功能完善;分析功能强大等优点。

逻辑分析仪主要的技术指标有:

* 最高采样频率:最高采样频率越高,捕获带宽越高。

* 通道数:通道数越多,能同时捕获的信号数也就越多。

* 存储深度:存储深度越大,能够记录的数据就越多。

* 输入阻抗:输入阻抗越高,对被测信号的影响越小。

* 触发方式:触发方式越多,使用起来越灵活。

其它技术指标还有:触发门限电平范围、是否有协议分析工具等等,这些都决定了逻辑分析仪的性能。

现在,逻辑分析仪的发展出现了两种趋势:传统逻辑分析仪和虚拟逻辑分析仪。传统逻辑分析仪功能强大,数据采集、分析和波形显示融于一身,但是价格十分昂贵;虚拟逻辑分析仪是PC技术和测量技术结合的产物,触发和记录功能由虚拟逻辑分析仪硬件完成,波形显示、输入设置等功能由PC机去完成,因此不会对逻辑分析仪性能造成影响,同时节省了显示和输入方面的成本,在开发工程师熟悉的Windows操作系统下工作操作起来更加方便。与传统逻辑分析仪相比虚拟逻辑分析仪具有质优价廉、方面使用等优点。

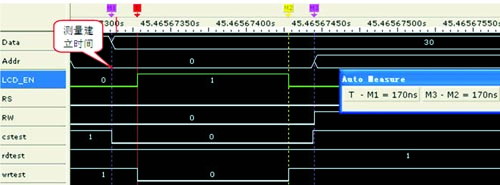

图1 液晶时序图

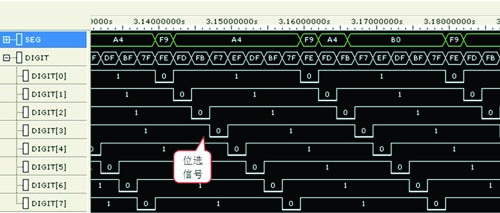

图2 驱动数码管的时序图

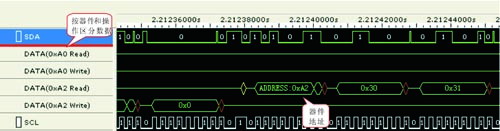

图3 读写E2PROM存储器时序图

图4 经I2C分析插件解码后的时序图

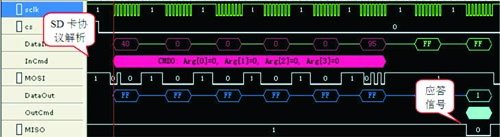

图5 SD卡CMD0命令时序图

本文使用广州致远电子有限公司生产LA1032逻辑分析仪进行测量,LA1032逻辑分析仪集成了逻辑分析、总线分析、协议分析、频率计、逻辑笔等多种测量分析功能,适用于各种数字电路的开发、测量、分析和调试工作。LA1032逻辑分析仪属于虚拟逻辑分析仪,性价比非常高。

应用

通常,嵌入式系统设计可以分为硬件部分和软件部分,从硬件电路的调试到驱动程序的测试几乎都需要逻辑分析仪的帮助。逻辑分析仪在嵌入式系统调试中的应用可以分为三个层次:

第一层:测试信号的时序和时间,这是逻辑分析仪最基本的应用;

第二层:利用逻辑分析协议分析的辅助功能,分析总线协议;

第三层:在线仿真器一起构成组合调试平台,调试驱动程序。

捕获毛刺

由于信号间延时不同,多路信号同时变化的瞬间往往会导致逻辑电路输出中一些不正确的尖峰信号,这些尖峰信号称为“毛刺”。另外,如果设备运行的环境比较恶劣,也会有高频信号串入电路,造成毛刺。如果让“毛刺”进入时钟、清零和置位等对毛刺敏感的输入端口,将会使电路产生不可预知的结果。

确定关键信号的建立时间和保持时间。

建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器;保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。

液晶既是一个慢速设备也是一个对时序很敏感的设备。如果数据的建立时间不够,很容易显示乱码。图1是利用逻辑分析仪捕获的液晶总线时序,并利用测量点来获取建立时间和保持时间的信息。

验证电路逻辑

电路设计好后,通常利用逻辑分析仪对输入输出信号进行采集分析,这样可以比较可靠的验证电路的逻辑功能。笔者为NiosII处理器设计了一个用于动态扫描8位数码管的IP核,由逻辑分析仪捕获的数据输出如图2所示。

分析总线协议

在确定关键信号路径上无“毛刺”干扰,且建立时间和保持时间符合器件时序要求后,下一步就是分析器件间是否能正常传输数据,即协议是否正确。MCU通过I2C总线对两个外部E2PROM存储器(器件地址分别是0xA0和0xA2)进行操作的时序图如所示。

若工程师要根据逻辑电平的高低进行人工分析,显然十分困难,更不要说区分哪些数据是发给E2PROM1的,哪些数据是发给E2PROM2的。这时,可以启动逻辑分析仪的I2C分析插件,分析结果的局部放大图如。

常见的总线分析插件还有SPI总线、UART、1-WIRE、CF协议分析等。插件的种类会因厂商的不同而不同。

配合调试工具单步调试程序

嵌入式系统的开发人员通常使用在线仿真器(ICE)来完成软件的调试,但随着嵌入式系统复杂性的提高,单纯的软件调试已经很难适应需求。在线仿真器+逻辑分析仪已经构成一种新的组合调试平台。借助逻辑分析仪可以发现许多隐匿很深的问题。例如,笔者在为NiosII处理器开发SD卡驱动的时候,遇到一个很奇怪的情况,SD卡命令已正确发送,逻辑分析仪也捕捉到了有效应答信号,如图5所示,但是程序仍然返回应答信号等待超时错误。

单步调试程序发现,虽然逻辑分析仪捕捉到了有效应答信号,但是由SPI核读入数据却是0x80,即SD卡忙。最后,问题的原因是,Altera公司提供的SPI核的CPOL=1,CPHA=0模式并不适合SD卡,将SPI核的工作模式设为CPOL=1,CPHA=1则驱动程序就可以正常工作了。

结语

综上所述,逻辑分析仪在嵌入式系统调试中的应用可以从基本数字电路的时序分析到器件间总线协议的分析,还以配合在线仿真器调试驱动软件。借助在线仿真器+逻辑分析仪这种新的调试平台,可以提高查找和解决问题的效率,增加产品的可靠性并能加快产品的上市速度。

评论