基于VSC8228的高速误码测试仪的设计*

摘要: 本文介绍了利用VSC8228完成高速误码检测的实现过程。通过实际使用表明:该方案的实现不仅廉价和使用方便,而且性能可靠。

本文引用地址:https://www.eepw.com.cn/article/80008.htm关键词: 误码测试;高速;重定时器;VSC8228

引言

在数字通信系统的性能测试中,通常使用误码测试仪对其误码性能进行测量。目前市面上已有多种误码测试仪。随着通信技术的不断发展,通信系统向着工作频率更高,信号处理更快的方向发展。在这种情况下,对于高速通信系统性能的检验,就需要高速误码率测试仪。国内厂家的产品,其信号处理速度较低,很难跟上现代通信系统的发展。国外的产品功能比较完善,处理速度很高,但其价格也相对较高。本文根据VITESSE公司的VSC8228芯片特点,提出一种可以方便地设计和制造价廉高速误码测试仪的方案,速度可达4.25Gbps。

VSC8228实现误码检测

VSC8228可提供的一个双通道重发器或重定时器,能应用于光纤信道、千兆比特以太网、SONETSDH以及无限带宽等多个领域。设备支持速率从125Mbps到4.25Gbps。利用获得的单一的时钟频率,该芯片可以将输入的串行数据在重定时器模式下与本地的参考时钟同步,或者在重发器模式下,与从输入数据中提取的时钟同步。在重定时器模式下,通过增加/减少弹性缓冲器插入/删除光纤信道填充字来调整输入数据与本地参考时钟的时序差异。

表1 piox与复用模式选项

VSC8228芯片主要分为四个主要部分:接收信道(RX),发送信道(TX),码型产生器与检测器,串行接口。当芯片应用于SGMII的标准时,接收信道能够提供一个从数据中提取的时钟,除了这种情况之外,接收信道和发送信道完全相同。每个信道都有一个输入缓冲器,时钟恢复单元,提供反馈和可编程的输出驱动。每个信道可以由各自的内部寄存器和硬件I/O口来独立控制。VSC8228的状态寄存器与控制寄存器的地址从00h到77h,一共128个寄存器,其中部分寄存器为VITESSE公司保留使用。通过设置相关寄存器,可以实现误码检测功能。

通过差分I/O口,片上输入/输出端接,输入均衡与输出去重,可以保持高度的信号完整性。可编程的输入均衡电路可以补偿PCB长线、背板、连接器和电缆上的频率限制。均衡、去重、输出驱动级、数据速率以及其他性能都是通过工业标准串行接口(Two-wire或者SPI)配置的。芯片内核与高速I/O口可以由一个1.2V的电源供电,也可是1.8V电源,或者两者一起供电。采用1.8V的电源供电是为了满足LVPECL输出摆动。为了兼容老化的控制器和专用集成电路(ASIC),TTL控制和标准I/O口可以由1.2V,1.8V,2.5V,3.3V电源中的任意一种供电。

从表1中可以看出,PIOx提供三种功能:SPI串行通信、I2C串行通信、引脚可编程模式。因此,可以利用SPI或者I2C总线来完成对VSC8228内部寄存器的设置,而通过对引脚可编程模式可以选择多种操作模式,比如环路,旁路,重定时或者重发,码型产生和检测。这些模式可以通过硬件引脚M0、M1、M2、M3或者内部芯片模式选择寄存器来控制。对于大部分模式,RX与TX都可以分别配置为重发器或者重定时器。而对于实际运用,一般将TX与RX信道同时配置为重发器或者重定时器。在重发模式下,串行数据进入CDR,在CDR中时钟从数据中提取出来,数据与恢复的时钟重新同步。而在重定时模式下,CDR的重定时功能将接收的串行数据与本地产生的参考时钟同步。

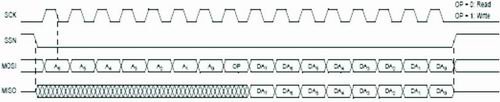

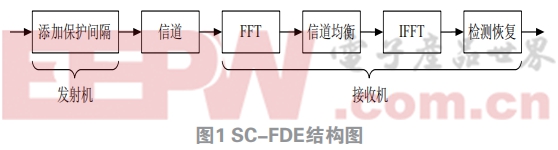

SPI通信时序如图1所示,SCK为SPI串行通信时钟信号,SSN为片选信号,低有效,MOSI为主出从入,MISO为主入从出,它们都与SCK的上升沿同步。在SPI通信时,先传输7位地址,后传输读写控制位OP,OP为0时表示读,OP为1时表示写,最后传输8位数据,故SPI通信的命令字长度为16位。

图1 SPI通信时序图

通过选择125M、106.25M、155M或者62.5M、53.125M、77.76M作为本地参考时钟频率,VSC8228可运用的领域有ESCON/SBCON、OC-3/OC-12/OC-48、快速及千兆比特以特网,以及光纤信道。故其速率最高可达4×Fibre Channel的4.25Gbps。

误码检测功能设置及BER计算

VSC8228的码型产生器与检测器可以产生与探测27 、 223、231的伪随机码,40 或 64比特用户定义码型以及光纤信号CRPAT、 CJTPAT 、CSPAT码型。错误掩码使能可以在码型产生端使某些位发生错误,也可以使检测端的某些比特产生错误,从而实现误码插入功能。码型产生器与码型检测器都是互相独立的。当芯片模式为引脚可编程模式,而M3、M2、M1、M0当设置为0001或者1100时,可以实现误码检测功能。而且此时,TX与RX信道都必须设置为Retimer模式,即重定时模式。

图2就是当M3、M2、M1、M0设置为0001时,时钟与数据的流向图,图中,绿线为数据流,蓝线为时钟。由图可知,PG模块(即码型产生器)产生的PBRS流从TXout流出,需检测的数据流从RXin输入,由于TX与RX信道都工作在Retimer模式,RX接收的数据将与本地时钟重新同步,同步后,数据流进入CHK模块进行误码检测。

图2 重定时模式下的码型产生器与检测器

VSC8228关于误码检测的寄存器有8个。寄存器为8比特宽,通过SPI或者I2C串行总线来设置各寄存器。

码型产生与码型检测以及自定义码型产生与自定义码型检测的码型必须设置一致。该芯片的误码计数器有32比特宽,可以计数高达43亿个误码。误码比较停止有两种模式:一种是检测的时间达到了检测时间设定寄存器里的设定的时间值;另一种是“自由比较”模式,在这种模式下,除非误码计数器记满或者用户强制停止,否则误码比较将永远比较下去。

为了计算BER,检测器有一个40比特的定时器。定时器的时钟周期为传输码流速率的1/16,在检测时间设定寄存器里设定测试时间,而检测时间读回寄存器里的值表示测试剩余时间,每经过一个时钟周期,读回寄存器里的值就减1。误码率是误码个数与总码个数的比值。总码个数是检测时间和速率的乘积。对不同的速率有不同的总数。计算测试时间与BER的公式如下:

![]() (1)

(1)

BER=误码个数= 误码个数

码总个数 码流速率×检测时间 (2)

其中,fs为系统时钟(串行传输码流速率)。

码型检测状态寄存器中的SYNC位在检测器与输入的码流同步之后就置1,FAIL位置1表示检测器探测到至少一个比特误码,而ECF位只有在误码计数器满了才会置1,如果SYNCERR位为1,则表示检测器还未与输入码流同步,而检测控制位已经清零,BUSY位在检测开始之后就一直为1。该位只有以下三种情况下才会清零:

·检测控制位清零,即检测停止命令;

·误码计数器记满;

·定时器的设定的检测时间到。

状态寄存器的各比特位联合表示的含义如表2所示。

表2 码型检测状态寄存器各比特的含义

误码测试仪的调试与实现

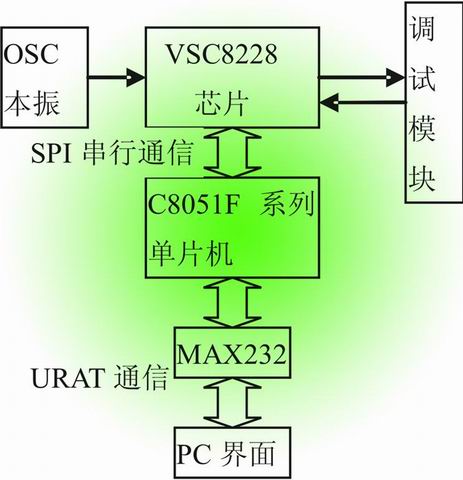

利用VSC8228芯片可以很方便的设计出一个廉价的高速误码测试仪。误码仪可分为两个独立的子系统:误码测试子系统和人机界面子系统。测试子系统由VSC8228芯片来实现。它完成伪随机码型的产生,同步及对比检测,计算出误码个数。人机界面子系统在整个测试系统中作为系统控制核心单元,通过人机界面完成系统作业。以C8051F系列单片机作为人机界面硬件的控制部分。对VSC8228芯片的控制、误码率的计算以及测试子系统的各状态的显示都通过PC机的界面来实现。PC界面可采用Delphi语言编写。

整个误码测试仪系统方框图如图3所示。

图3 误码测试仪系统方框图

由于本误码测试仪的工作速率较高,故必须选择高精度的晶振作为本地参考时钟。在开发中,目前选取的晶振是VECTRON公司的VCC6-QAB-125M00,其频偏小于100ppm,上升时间与下降时间都在2ns左右。

C8051F005单片机是完全集成的混合信号系统级芯片(SoC),具有与8051兼容的高速CIP-51内核,片内集成了数据采集和控制系统中常用的模拟、数字外设及其他功能部件。内置FLASH程序存储器、内部RAM,大部分器件内部还有位于外部数据存储器空间的RAM,即XRAM,有I2C/SMBus、UART、SPI串行接口。C8051F005单片机具有片内调试电路,通过JTAG接口可以进行非侵入式、全速的在系统调试。

误码测试仪的实现过程如下:PC界面通过RS232串口实现与C8051F005的通信,将对VSC8228各寄存器的设置发送给F005单片机,每个控制命令为16比特;单片机通过SPI口将上位机发送过来的控制命令转发给VSC8228,完成VSC8228的各寄存器的设置。在将8228从SPI通信模式转到引脚可编程模式后,VSC8228产生PBRS(自定义码型或光纤信道码流),码流经调试模块后,输入到VSC8228的码型检测端,检测端开始进行同步,同步完成后,就开始检测误码,并将整个工作过程中的各种状态通过检测状态寄存器以及其他状态寄存器显示出来。为了实时的显示误码仪的工作状态,单片机每秒扫描一次各寄存器,将其值通过RS232串口上传到PC界面。

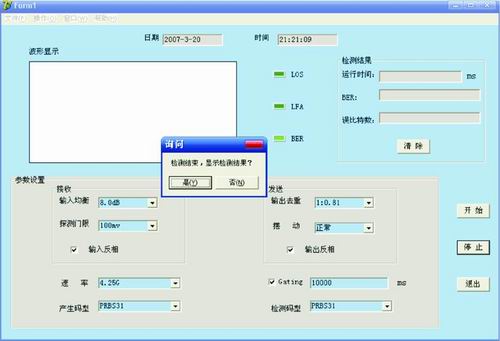

图4 误码测试仪PC界面

本误码议的界面开发,主要基于Delphi平台。主要采用Delphi的spcomm组件来实现串口通信。它主要实现以下功能:显示当前日期和时间、根据检测需要设置检测参数(产生码型、检测码型、速率、输出去重、摆动输入均衡、探测门限等)、运行时间及BER的计算、控制按钮及LED显示检测状态。状态灯可以显示的状态有“无信号”,“同步态”“失同步态”与“等待态”等。

由于该误码仪的工作频率可高达4.25Gbps,故在电路设计中需特别考虑信号完整性问题,严格按高速PCB电路设计方法来进行设计,如合理的端接,布4层PCB板,利用candence软件对于关键线路进行仿真等。在本误码仪的调试过程中,遇到的问题也主要是由于信号的速度快而引起的。

目前本方案的误码检测仪已运用于EPON光收发模块的连续码测试,在与台湾宜捷威科技的FMTS-3000以及安立的MP1630的测试比较结果看,本方案的误码仪其误码数量级与上述两种设备基本一致,但是不能支持突发误码的测试。对突发误码测试的支持是项目组下一步研究的目标。

结语

VSC8228芯片支持多种速率,内置PBRS及其他码型的产生及探测模块,本文利用该特点设计出一种廉价的高速误码仪,其测试码型有27 、223、231的伪随机码,40或64比特用户定义码型以及光纤信号CRPAT、CJTPAT、CSPAT码型,一次可测误码高达43亿个,测码速高达4.25Gbps。在EPON光收发模块中实现了误码测试,取得较好的效果,而且功耗低。

参考文献:

1. Vitesse Inc.VSC8228 datasheet.www.vitesse.com

2. Yongquan Fan, Zeljko Zilic,and Man Wah Chiang.A Versatile High Speed Bit Error Rate Testing Scheme.Quality Electronic Design, 2004. Proceedings. 5th International Symposium on,IEEE2004:395-400

3. Wei-Zen Chen;Guan-Sheng Huang.A parallel multi-pattern PRBS generator and BER tester for 40/sup +/ Gbps Serdes applications.Advanced System Integrated Circuits 2004. Proceedings of 2004 IEEE Asia-Pacific Conference on. Aug 2004 Page(s):318-321

4. Sharawi, M.S.Practical issues in high speed PCB design.Potentials,IEEE,Volume 23,Issue 2,Apr-May 2004 Page(s):24~27

5. 陈伟、刘会衡、黄秋元,EPON突发式光信号产生及测试系统设计,武汉理工大学学报2005.27(10),86-88

adc相关文章:adc是什么

尘埃粒子计数器相关文章:尘埃粒子计数器原理 晶振相关文章:晶振原理 网线测试仪相关文章:网线测试仪原理

评论