设计安全否?

设计安全否?

Is it safe?

Philip Ling

对于海外制造来说,设计的安全性是关键。

对各行各业来说,失窃都是一个严重的问题,但设计的被盗会造成极大的经济损失;对于资源有限的公司来说,它可能是灾难性的。

然而,海外制造——人们都知道它本质上对设计的安全性构成了威胁——依然存在,部分原因是它使资源有限的公司能角逐全球市场。设计公司倾向于采用标准化的部件,因而其知识产权无法从本质上深埋到一个芯片中,这一点加深了上述对立的两方面(设计安全性的降低与全球市场的竞争力)之间的矛盾。因此,对一个设计实施逆向工程并生产出功能相同的产品就变得相对容易。

以这种方式盗用IP,是设计被盗方面的一个例子,令人吃惊的是,在某些领域中,也是可以容忍的。另一种方式则是过度制造——合同承包制造商制造的产品数量超出客户要求其制造的数量,而制造商将多余的产品以较低的价格在“灰色”市场上出售。也许最卑劣的设计偷窃形式是克隆——不仅仅是功能的复制,而是设计的本身的复制,连最后一个字节都不放过。然后,利用在公开市场上能合法采购到的部件来繁殖出相应的设计。

上述的最后一种实例对设计的合法拥有者提出的挑战也许是最大的,特别是当设计主要由软件来定义的时候,因为,要证明发生了上述有意的欺诈或者专利权的侵犯是十分困难的。FPGA的制造商们正是将其努力集中在此处,他们现在将对设计的保护视为一种重要的、体现其鲜明特色的功能特性。

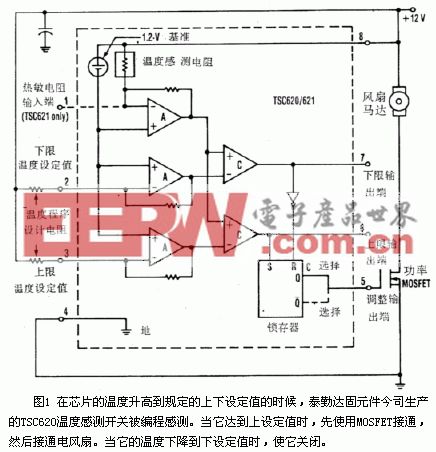

努力的目标正是保护配置的比特流——在基于SRAM的部件中,它将会储存在一个外部的非易失性存储中。如果定义配置的比特流在调往FPGA的途中被截获,作奸犯科者可以对代码实施逆向工程,从而获取设计,或者,更简单的是,用它来配置另一种器件,而无需明白它的工作原理。对数据进行加密则意味着,当它被截获时,如果没有密钥就毫无意义,设计的保密性仍得到保证。

代码的破解

Xilinx是第一家利用Triple DES(数据加密标准)实现数据加密的厂商。该标准基于DES而建立,使用了56bit的加密密钥。它已被军方和其他领域所采用,时间以长达20年,直到被证明是可以被破解的为止(参见图框中的背景介绍)。该解决方案是用两个密钥将DES重复3次——3重DES。当Xilinx决定将加密技术嵌入Virtex II系列中时,这是为人们所接受的、得以应用的安全保密标准。各密钥存储到器件中的易失性存储中,这样做有其自身的考虑。尽管这意味着如有必要可替换密钥,但也意味着需要采用外部的后备电源(一般是电池),以防备电源被切断时密钥不至于丢失。这种方法为Xilinx的竞争者所诟病,但只是到最近一段时间才有人提出了一种替代方案。

去年,Altera推出了Stratix II,它是首款能在FPGA架构中以硬连线方式实现先进加密标准(AES)算法的FPGA。这些方法的关键,确切的说,是密钥——在这个实例中,就是用于对数据进行加密的128bit AES密钥。

背景介绍

AES

根据美国政府的分类,AES广泛用于“敏感但不保密”的信息。“联邦信息处理标准”公文192公布了相应的标准,它通过称为Rijndael的算法来实现,这种算法从5种算法中选出。

它取代了数据加密标准(DES),该标准采用56bit的密钥。虽然DES存在了接近20年的时间,但并行处理方面的进步使得它最终遭到破解,人们决定,需要采用一种更为安全的标准。

美国国家标准与技术局的计算机安全资源中心于1999年正式公开征集算法,而最终选中了5种候选方案。所有这些方案的算法采用了块密码,也就是说,它们一次对一个数据块进行运算,处理的遍数预先给定。AES提供了128、192和256bit的密钥,虽然大多数商业实现方案采用128bit,因为即使这样的大小,其安全性也比DES要高出许多倍。为了理解这一点,不妨设想一个强大到足以在1s内破解DES密钥的海量并行处理机(在当今是无法实现的),据估计,这样的一台机器要花上149万亿年才能破解一个128bit的AES密钥。相比之下,宇宙的寿命也不过有200亿年的历史。

配置代码的加密通过Altera的编程环境Quartus II来完成,而密钥则被烧入器件内部只能编程一次的内存中。这可以由Altera公司来完成,或者在现场实现,虽然Altera承认,目前是由它来完成这一过程以确保其可靠性。

后勤供应方面的恶梦?

这里存在的危险是客户会大批订购器件而“丢失”密钥——使得整批库存不可用。此外,由于每一个器件采用唯一的一个密钥,这也使得每个FPGA及其相应的配置器件独一无二——很显然是一种非常安全的解决方案,但会给后勤供应带来巨大的麻烦。

近来,Actel推出了ProAsic3系列,它还在FPGA架构中嵌入了一个128bit密钥AES解密引擎。该公司相信,这是第一款能提供AES解密的“超值” (低价)FPGA,其安全性功能和低成本的特性使之成为工程师实难割舍的最爱。

基于SRAM的FPGA对AES加密配置数据的需求是显而易见的——配置代码储存在芯片之外。而Actel的ProAsic3系列则是基于闪存的,在这种情况下,它的重要性势必有所降低。不过,Actel的闪存器营销主管Martin Mason相信:“在基于价值的市场上,安全性更为重要。”

虽然该公司的防熔断技术的性能和安全性方面仍然是终极的解决之道,Mason还是宣称闪存是两者中成本经济性更好的一种。AES密钥应该在安全的、或者可信任的编程中心中完成编程,可以安全地存储在专用的、无法被读取的闪存器中。与其它方案一样,是由设计软件以同一密钥来进行加密的。

你必须掌握密钥

Actel系列的一个附加的功能特性是消息的认证控制机制,如果密钥不匹配的话,它们可以防止配置数据对架构进行编程。

此外,在AES功能激活以前,以总钥(pass key)形式还可以实现更高层次的安全性——必须输入它才能访问器件。用户可以用总钥锁闭器件或者解锁器件;器件被锁住时,无法访问FPGA,这样器件写入、检验和擦除等功能都被禁用。该系列产品均不支持回读(read back)机制。

配置数据在本器件内进行的加密,将使得克隆变得更为困难,因为,即使作奸者可以获取配置数据,如果没有正确的密钥的话,它也是无用的。

虽然芯片厂商们正在试图从正面解决安全性问题,但开发者需要完成若干步骤,才能使得软件也变得更为安全,如电子水印或者嵌入式序列号。不过,归根结底,这只是些需要依赖法治手段来维护的、威慑性的措施而已。也许人们真正需要的,是可以运用于外部程序存储而不会对总的系统性能造成负面影响的AES版本。

评论