最新SMT复杂技术

只要关注一下如今在各地举办的形形色色的专业会议的主题,我们就不难了解电子产品中采用了哪些最新技术。CSP、0201无源元件、无铅焊接和光电子,可以说是近来许多公司在PCB上实践和积极评价的热门先进技术。

比如说,如何处理在CSP和0201组装中常见的超小开孔(250um)问题,就是焊膏印刷以前从未有过的基本物理问题。板级光电子组装,作为通信和网络技术中发展起来的一大领域,其工艺非常精细。典型封装昂贵而易损坏,特别是在器件引线成形之后。

这些复杂技术的设计指导原则也与普通SMT工艺有很大差异,因为在确保组装生产率和产品可靠性方面,板设计扮演着更为重要的角色;例如,对CSP焊接互连来说,仅仅通过改变板键合盘尺寸,就能明显提高可靠性。

CSP应用

如今人们常见的一种关键技术是CSP(图1)。CSP技术的魅力在于它具有诸多优点,如减小封装尺寸、增加针数、功能∕性能增强以及封装的可返工性等。CSP的高效优点体现在:用于板级组装时,能够跨出细间距(细至0.075mm)周边封装的界限,进入较大间距(1,0.8,0.75,0.5,0.4mm)区域阵列结构。

已有许多CSP器件在消费类电信领域应用多年了,人们普遍认为它们是SRAM与DRAM、中等针数ASIC、快闪存储器和微处理器领域的低成本解决方案。CSP可以有四种基本特征形式:即刚性基、柔性基、引线框架基和晶片级规模。CSP技术可以取代SOIC和QFP器件而成为主流组件技术。

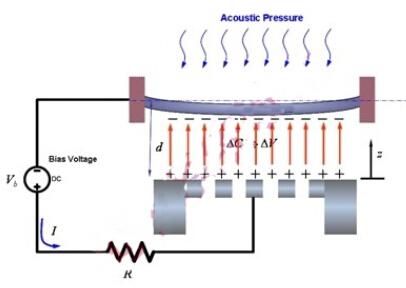

CSP组装工艺有一个问题,就是焊接互连的键合盘很小。通常0.5mm间距CSP的键合盘尺寸为0.250~0.275mm。如此小的尺寸,通过面积比为0.6甚至更低的开口印刷焊膏是很困难的。不过,采用精心设计的工艺,可成功地进行印刷。而故障的发生通常是因为模板开口堵塞引起的焊料不足。板级可靠性主要取决于封装类型,而CSP器件平均能经受-40~125℃的热周期800~1200次,可以无需下填充。然而,如果采用下填充材料,大多数CSP的热可靠性能增加300%。CSP器件故障一般与焊料疲劳开裂有关。

无源元件的进步

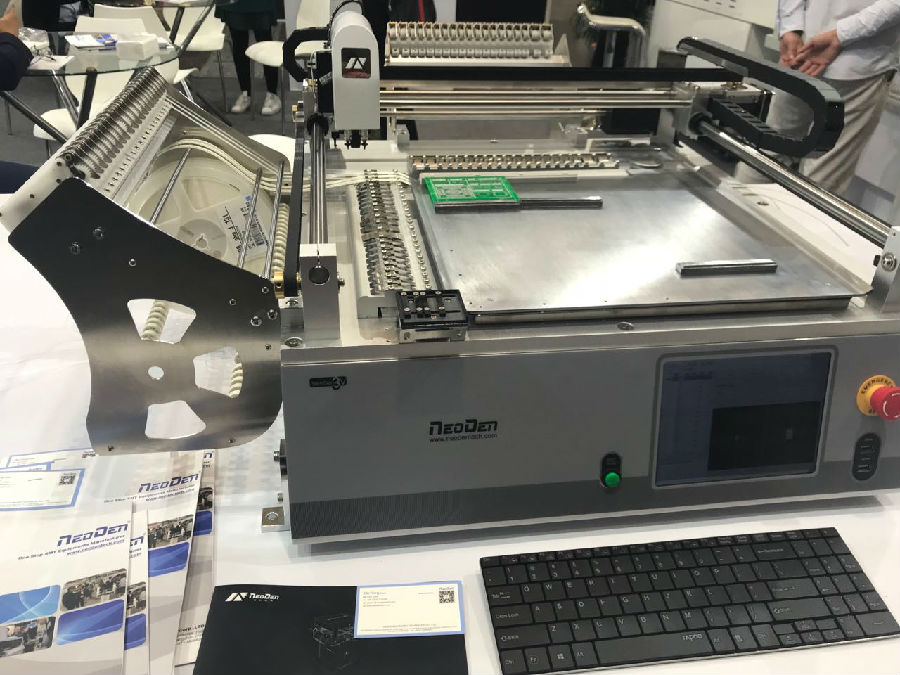

另一大新兴领域是0201无源元件技术,由于减小板尺寸的市场需要,人们对0201元件十分关注。自从1999年中期0201元件推出,蜂窝电话制造商就把它们与CSP一起组装到电话中,印板尺寸由此至少减小一半。处理这类封装相当麻烦,要减少工艺后缺陷(如桥接和直立)的出现,焊盘尺寸最优化和元件间距是关键。只要设计合理,这些封装可以紧贴着放置,间距可小至150?m。

另外,0201器件能贴放到BGA和较大的CSP下方。图2是在有0.8mm间距的14mm CSP组件下面的0201的横截面图。由于这些小型分立元件的尺寸很小,组装设备厂家已计划开发更新的系统与0201相兼容。

通孔组装仍有生命力

光电子封装正广泛应用于高速数据传送盛行的电信和网络领域。普通板级光电子器件是“蝴蝶形”模块。这些器件的典型引线从封装四边伸出并水平扩展。其组装方法与通孔元器件相同,通常采用手工工艺—-引线经引线成型压力工具处理并插入印板通路孔贯穿基板。

处理这类器件的主要问题是,在引线成型工艺期间可能发生的引线损坏。由于这类封装都很昂贵,必须小心处理,以免引线被成型操作损坏或引线-器件体连接口处模块封装断裂。归根结底,把光电子元器件结合到标准SMT产品中的最佳解决方案是采用自动设备,这样从盘中取出元器件,放在引线成型工具上,之后再把带引线的器件从成型机上取出,最后把模块放在印板上。鉴于这种选择要求相当大资本的设备投资,大多数公司还会继续选择手工组装工艺。

大尺寸印板(20

评论