Stratix III FPGA的设计安全特性

——

Stratix III器件中的设计安全性实现

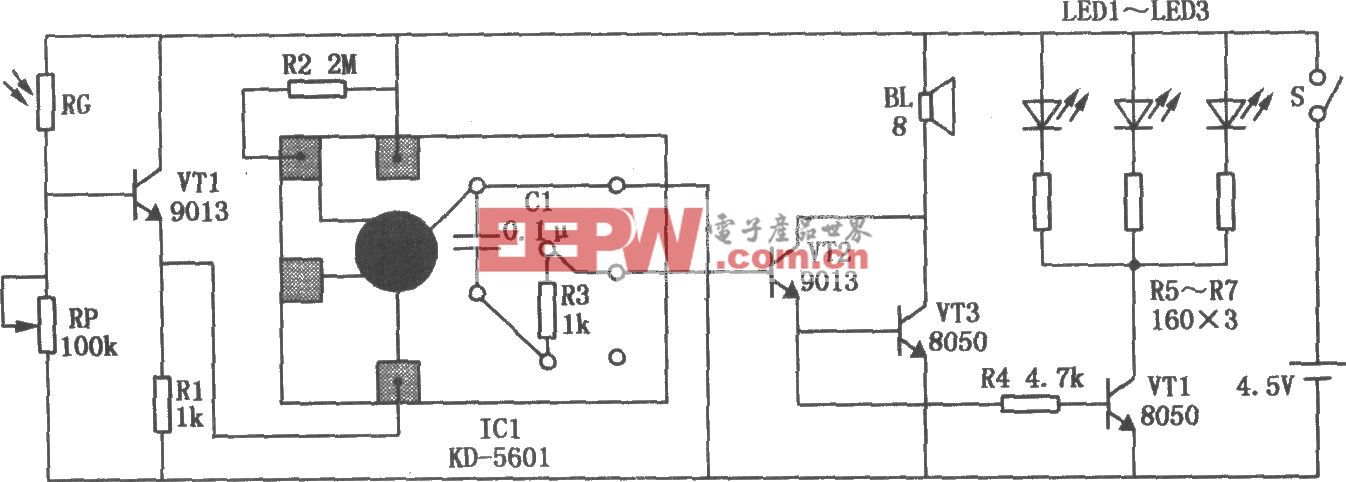

基于SRAM的FPGA具有易失性,需要在上电时将配置比特流从闪存或者配置器件送至FPGA。这种配置比特流在传输过程中会被截取。为保证设计安全性,Altera Stratix III采用高级加密标准(AES)和256位密钥对配置比特流进行加密。图1所示为安全配置流程,它包括三个步骤:

用户定义的 AES 密钥被设置在Stratix III 器件的非易失密钥存储中。

Quartus® II 软件使用相同的AES密钥产生一个加密配置文件,然后将其存储在外部闪存或者配置器件中。

上电时,闪存或者配置器件将加密配置文件发送给Stratix III,利用存储的AES密钥解密文件,进行配置。

图1. Stratix III FPGA安全配置流程

AES是联邦信息处理标准 ( FIPS-197 [PDF]),经过认证,美国政府组织利用这一技术保护敏感的、未列入密级的信息。全球范围内商业系统也广泛采用了该标准。Stratix II AES实施方案经认证,符合FIPS-197标准。

为了给设计人员提供更多的选择,Stratix III FPGA同时提供易失和非易失安全密钥存储。易失安全密钥存储更加灵活,而非易失安全密钥存储更加实用。表1对比了易失和非易失密钥存储。

|

表 1. 易失和非易失密钥对比 | ||

|

|

易失密钥 |

非易失密钥 |

|

密钥长度 |

256位 |

256位 |

|

密钥可编程性 |

可重新编程,能够擦除 |

一次可编程 |

|

外部电池 |

需要 |

不需要 |

|

密钥编程方法 |

板上 |

板上和板下 |

|

设计保护 |

防止被复制和反向剖析 |

防止被复制、反向剖析和篡改 |

Stratix III FPGA 设计安全特性的应用

包括重要 IP 或者敏感信息的产品可以充分利用 Stratix III 设计安全特性,从中受益。以下列出了一些应用实例:

- 产品在 IP 法律还没有很好实行的地区进行生产或者销售时—— Stratix III FPGA 内置设计安全特性保护了设计人员的 IP 、收益和竞争优势。

- 产品版本控制和定制—— 在 Stratix III 不同器件中可以设置不同的安全密钥,提供产品版本控制和定制。

- 需要版税的商业模型—— IP 供应商在安全 Stratix III FPGA 中通过加密配置文件交付 IP 时,可以确保其 IP 版税收益。由于只有含有正确密钥的 Stratix III FPGA 能够使用加密配置文件,因此, IP 供应商可以一直跟踪 IP 使用的具体数量。

- 安全功能—— 在采用了安全功能的系统中, Stratix III FPGA 提供器件级安全特性。

- 游戏应用—— Stratix III 设计安全特性的篡改保护功能可以保护对游戏机或者赌博机的无意修改。

- 军事防篡改—— Stratix III FPGA 应用于保护军事技术和信息。

- 测试市场 ASSP —— ASSP 利用安全 Stratix III FPGA 作为 ASSP 芯片,配合加密配置文件,测试其 ASSP 的市场情况以及功能。由于只有含有正确密钥的 Stratix III FPGA 能够使用加密配置文件,因此, IP 供应商能够一直控制 IP 。

评论