DDS逻辑优化设计及Verilog实现

摘 要:本文主要介绍了在DDS系统中,为了提高芯片运算速度,加大输出带宽,减小芯片规模从而提高可靠性和频谱纯度而采用的优化方法及其VerilogHDL实现。

关键词:流水线;输入寄存器结构;加法器最低位修正;压缩存储查找表

概述

由于DDS频率合成方法具有低频率转换时间、低失真输出波形、高分辨率、高频谱纯度、可编程和宽频率输出范围等优良性能,在现代频率合成领域中具有越来越重要的地位。在许多应用领域中,如通信、导航、雷达和电子对抗等, DDS频率源都是主流的关键部件。

DDS的改进构想

DDS电路的关键是利用高速存储器做查找表,通过高速DAC产生已经以数字形式存入的正弦波,并用频率控制字K来调制DDS的输出频率。

从算法可以看出,DDS的工作主频决定它输出的频率:fout=fclk*K/2N(N为相位累加器的位数,K为频率控制字,位宽32位,fclk是芯片主频),所以提高DDS的主频就可以提高它的输出频率和输出带宽,同时对于ROM的实现来说,如果用32根地址线来寻址,则需要一个非常大的ROM,要232那么大。这种ROM从存取时间、可靠性和制造上来说是不实际的,所以要对算法进行改进。

DDS设计优化

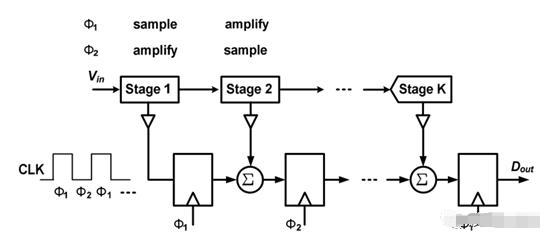

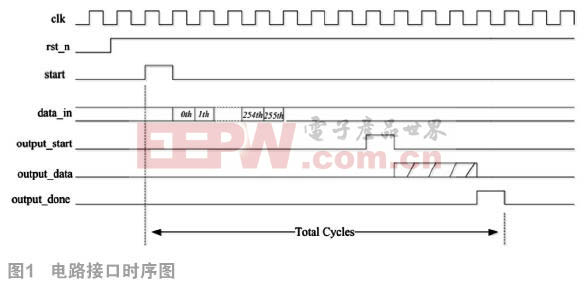

这一部分对DDS设计进行了优化,目的是在保持其原有优点的基础上,尽量减少硬件复杂性,降低芯片面积和功耗等,提高芯片速度。核心结构如图1所示。图中相位累加器为32位,如果主频为75MHz,则确定频率分辨率为0.0174Hz。相位-幅值转换部分由查找表逻辑实现。查找表用字长为13位的ROM实现,存储压缩后的SIN值。本芯片在相位累加器和查找表之间插入了一个地址转换器,负责进行地址转换。在查找表和DAC之间插入了一个数据转换器,负责进行数据转换。相位累加器输出的地址码位宽为16位, Data[12:0]为查找表输出的二进制SIN值,它经过数据转换器后和adri[15]反拼接成14位数据输入DAC,变换成连续的正弦信号V输出。

对DDS优化如下:

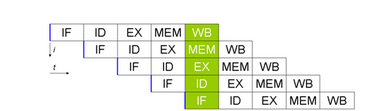

1. 引入流水线对累加器进行优化。将32位累加器分成4条流水线,每条流水线完成8位的加法运算,流水线的进位进行级联。运用流水线实现加法器可以提高累加器的运算速度3倍之多。为了提高运算速度,加法器算法采用的是目前速度最快的预先进位算法。为了避免因预先进位加法器中进位传输链过长而影响速度,每8位加法器由两个4位的预先进位加法器级联而成。因引入流水线而多加入80个寄存器中的48个可以通过改进的输入数据寄存器减少,详见图2。对输入寄存器结构进行优化,以降低硬件复杂度,减小芯片面积,从而进一步提高运行速度。在设计中增加一个时钟分配器,通过时钟的分配时序,可以节省保存输入频率控制字的级联寄存器。还同时节约芯片的24个I/O口,唯一的缺点是数据要保持4个时钟周期,会降低系统跳频的跳转频率。

2. 从图1可知,从相位累加器的32位输出中提取高16位作为ROM的查找地址,相位累加器的输出截尾可以减少ROM的尺寸到原来的1/216,把ROM容量的单元数从232降到216。损失的低16位相位累加数值对应0.02度的间断,在绝大部分应用中都是可以忽略的,在生成波形的精确度上已经可以满足要求了。但由此而产生的截尾误差却会对频谱纯度和输出带宽产生影响。相应的解决办法如图3所示:将D触发器的输出端连接到相位累加器最低位的c0,相位累加器字长变为32+1位,频率控制字的值相当于2K+1,而截尾误差为2,即频率控制字(奇数)和截尾误差(2的整数次幂)之间互质。这样带来的地址上1/2LSB的误差影响,在实际应用中可以忽略。

主要优化算法的Verilog实现

VerilogHDL语言专门面向硬件与系统设计。可以在芯片算法、功能模块、层次结构和测试向量等方面进行描述。VerilogHDL简单、灵活,可直接描述硬件单元结构,而且具有很好的可读性。

流水线加法器阵列和加法器最低进位修正实现

dffn gate1(ci,ci,clk,rst);

lineadd gate2(q[7:0],co0,ci,clk1, clk,datain,k,rst);

twolineadd gate3(q[15:8],co1, co0,clk2,clk,k,rst);

trilineadd gate4(q[23:16], co2,net1,net3, co1,clk3,clk,k,rst);

forlineadd gate5(q[31:24],co,co2, clk4,clk,k,rst);

这是用VerilogHDL的结构描述方法实现的,对应于用电路图输入逻辑。其中的lineadd,twolineadd, trilineadd,forlineadd是带寄存器的加法器流水线。Dffn是输出为QN的D触发器,其输出端接加法器最低进位。

波形折叠及抬高算法

波形折叠(地址转换器)

always@(adri)

if(adri[14])

adro=14'h1fff^adri[13:0];

else

adro=adri;

根据adri[14]的数值可以判断地址码是否需要对p/2进行折叠。这里用^是按位异或,作用是用全1减去adri值,从而实现地址码对p/2的折叠。因为被减数是确定的而且是全1,所以可以用异或实现减法,这样比用减法器要节约门数。

抬高算法(数据转换器)

always@(data,adri[15])

begin

if(adri[15])

datum=13'h3fff^data;

else

{datum}=data-13'h0001;

end

result={ !adri[15],datum};

end

根据adri[15]的数值可以判断波形值应该是正是负,如果是正,则用全1和从ROM中取出的数相加,就相当于原数据减1后再在最高位拼接1,以1LSB的偏移量为代价,可以省略减法器。如果是负,则用按位异或实现相减,得到经过抬高处理的数据。抬高处理是为了满足DAC的输入全为正值的需要。

压缩sin值ROM查找表逻辑的结构描述实现

ROM1 gate1(daone,adro[13:5], clk,ren,dinone);

ROM2 gate2(datwo,{adro[13:9], adro[4:0]},clk,ren,dintwo);

adderone gate3(daone, datwo,result[11:0]);

addertwo gate4(adro[13:5], result[11:0],data[12:0]

ROM1和ROM2是两个读写存储器,ROM1是主值存储器,ROM2是修正存储器,分别存放预先计算好的主值和修正值。dinone和dintow是ROM的数据写入端,daone和datwo是数据读出端。Allader是一个12位加法器,将主值和修正值相加。addertwo是13位加法器,完成 [Sin(p x/2)-p x/2]+p x/2,从而得到Sin(p x/2)的值。

结语

总体而言,DDS可以得到下面的改进:使用流水线算法和输入数据寄存器可以在不过多增加门数的条件下,大幅提高芯片的工作频率;修正加法器最低进位位带来3dB左右的频谱性能提高,提高了输出波形的频谱纯度;而压缩存储查找表在保证芯片使用精度的情况下减少了大部分面积,利用SIN函数的对称性和三角恒等式以及最后的SIN值压缩算法经过具体实验可以达到79.24:1的压缩率,大大节约了ROM的容量,可以使芯片在满足性能要求的基础上,节约相当大的芯片面积,同时节约了功耗提高了芯片的可靠性。按照此优化方法设计的芯片可以工作在75MHz频率上,输出信号谐波小于-60dB,而芯片规模是13000门左右。■

参考文献

1 J Vankka, M Waltari, and M Kosunen, 褹 Direct Digital Synthesizer with an On-chip D/A-Converter? IEEE JSolStaCirc,1998;33(2):218-227

2 J. Vankka, 襍pur Reduction Techniques in Sine Output Direct Digital Synthesis?, in Proc. 1996 IEEE Frequency Control Symp., June 1996; 951?59

3 S. Mortezapour, E. K. F. Lee, 褼esign of Low-Power ROM-Less Direct Digital Frequency Synthesizer Using Nonlinear Digital-to-Analog Converter?on IEEE Journal of Solid-State Circuits,Vol. 34, No. 10, October 1999:1350-1359

4. L. K. Tan and H. Samueli, “A 200 MHz Quadrature Digital Synthesizer/Mixer in 0.8mm CMOS” on IEEE Journal of Solid-State Circuits Vol. 30, No. 3, March 1995:193-200

评论