频率匹配的原理及其硬件实现

摘 要:本文介绍了一种信号检测的方法——频率匹配,文中详细地叙述了频率匹配算法的原理,用 Matlab 从理论上证明了算法的正确性, 在此基础上用可综合的RTL Verilog模型描述了算法,通过对综合后网表进行仿真,验证了频率匹配算法硬件实现的可行性。最后,根据频率匹配的原理,实现了一种高精度数字频率检测器,并给出了相关的精度值。

关键词:信号检测;频率匹配;Matlab;高精度频率检测器

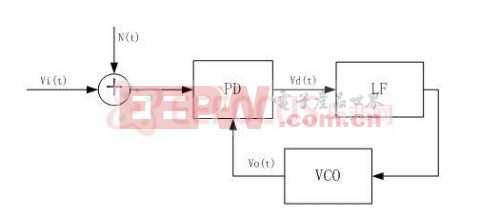

图 1 实现频率匹配算法的结构框图

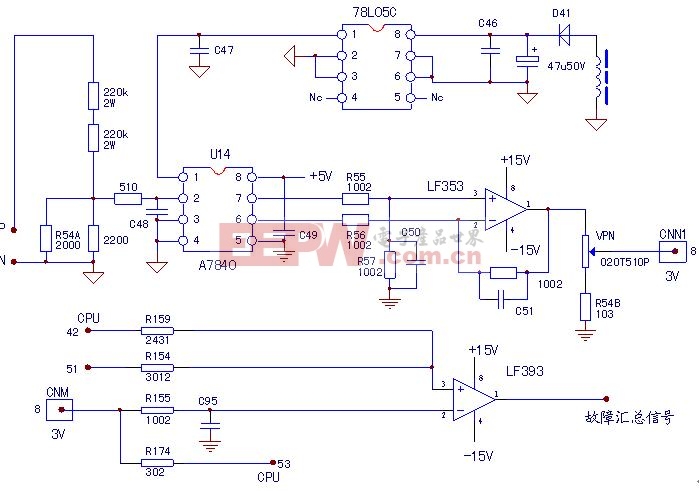

图2 频率匹配算法模块的内部结构

前言

对于未知信号,可以通过傅立叶变换来检测信号中的频谱分布情况。但是,从傅立叶变换的结果只能看出该信号中包含哪些频率,而对于某频率的幅度在时域的分布情况却无从知晓,为了弄清楚某一频率的幅度在时域的分布情况,可以通过频率匹配来测定。同样,如果知道某一信号中包含某一频率,也可以通过频率匹配将信号中该频率的幅度所在的时域检测出来。

所谓频率匹配就是使用一种频率的信号(以下称之为匹配信号)去与未知信号(以下称之为被匹配信号)进行相关运算。因为相关运算可以用来检测两个信号的相似性,而做相关运算的目的就是将被匹配信号中与匹配信号频率相同或相近的部分进行放大,这样就可以弄清楚与匹配信号频率相同或相近的频率在被匹配信号中的分布情况。匹配信号必须是一种单一频率的信号,因此最理想的匹配信号当然就是三角函数。本文就以三角函数为例,叙述频率匹配的原理和方法。

频率匹配的实现方法

实际应用中的信号通常是离散的,因此,本文只讨论离散信号。可以用频率匹配来实现离散信号的检测、识别和提取。下面介绍离散信号频率匹配的实现方法。

设被匹配离散信号为 X(m),其采样频率为 fs,取匹配离散信号为 和,离散信号的频率匹配运算如下:

(1)

(2)

(3)

其中 N 根据实际情况而定,通常取的整数倍。

通过匹配运算得到的离散函数 M(n),具有如下性质:若 X(n) 在区间[n1,n2] 上的频率为w,则 M(n) 在区间[n1,n2]上将出现峰值,即在区间[n1,n2] 内 M(n) 的值将明显大于其它地方的值。

频率匹配的 DSP 实现

下面简要地介绍频率匹配的 DSP 实现方法,频率匹配算法的主要部分是计算 M1(n) 和 M2(n) 。频率匹配的 DSP 实现方法可以分成两种:单采样和块采样。在单采样模式中,每一个采样周期内只有一个采样值到达,在每一个采样周期内也只产生一个信号输出值。因此,单采样实现的频率匹配必须实时执行。在块采样模式中,每一个块周期内有多个采样值到达,且每一个块周期内能产生多个信号输出值。块采样能够根据实际需要,既可以很快也可以很慢地处理所有输入采样值。

在这里将使用块采样模式来实现频率匹配,为了节省存储器和软件开销,大多数 DSP 硬件都可实现循环存储器,此处的频率匹配 DSP也使用循环缓冲器来实现。对于输入的新的采样值,采用新的采样值进入、老的采样值溢出的方式,这样可以节省软件开销。频率匹配的 DSP 实现需要 3 个循环缓冲器,用来分别存储 X(n)、sin(n) 和cos(n) 。其中 X(n) 在每一个块周期内需要接收多个采样值,在新的采样值进入循环缓冲器时,溢出老的采样值。由于sin(n) 和cos(n) 是周期函数,因此不需要在每个块周期都向其循环缓冲器输入采样值,只需在第一个块周期内将一个周期的采样值存到缓冲器中即可。在处理过程中,在每一个块周期内,不需要再向循环缓冲器中装载 sin(n) 和cos(n) 的值,只需更新循环缓冲器的变址器指针即可,而对于 X(n) 循环缓冲器,每一个块周期都要向其中输入新的采样值,并且需要更新循环缓冲器的变址器指针。

为了理解上述实现思想,举一个简单的例子:设采样的块长度为 4,做相关运算的点数为 5,保存X(n) 值的循环缓冲器长度为 8;设三角离散函数的周期为 5(在实际应用中,通常取做相关运算的点数 = 三角离散函数的周期),考虑到循环缓冲器的长度必须是 2 的幂次,所以保存sin(n) 和 cos(n) 的循环缓冲器的长度也取 8。在第一个块周期内,第一次输出集合{M1(0),M1(1), M1(2),M1(3) }按下式计算: (4)

从式(4)可以看出,在第一个块周期内,需要从缓冲器得到 8 个采样值X(0)~X(7)。同理可以推出在第二个块周期内,需要从缓冲器得到X(4)~X(11),在第三个块周期内,需要从缓冲器得到X(8)~X(15)。因此在第二个块周期后,应按顺序向循环缓冲器中装入4个新的采样值。一个块周期开始时,循环缓冲器的变址器指针总是指向在该块周期内使用的第一个采样值,因此 X(n) 的循环缓冲器变址指针应该按照式(5)来计算。

变址器指针=[前一个变指针 + 块长度] mod 缓冲器长度 (5)

由于sin(n)是周期为 5 的函数,因此只需在第一个块周期内向sin(n)的循环缓冲器装载 5 个采样值。sin(n)的循环缓冲器变址指针应该按照式(6)来计算。

变址器指针=[前一个变指针 + 块长度] mod 三角离散函数的周期 (6)

在计算M2(n)时,X(n)循环缓冲器实现方法如前面所述,cos(n)循环缓冲器的实现方法与sin(n)的循环缓冲器相同,其循环缓冲器变址指针计算也遵循式 (6)。

使用 Verilog HDL实现频率

匹配算法

频率匹配算法并不是很复杂,因此可以使用 Verilog HDL实现该算法,然后将生成的网表文件下载到 FPGA中。使用 Verilog HDL实现频率匹配算法的结构框图如图 1所示。

图1包含了两个模块,其中数据转换缓存器的作用是实现数据格式转换和数据缓存,数据格式转换是将从外部接收到数据的格式转换成频率匹配算法模块可以处理的数据格式,数据缓存就是将接收到的大量数据存到寄存器中,然后在每个时钟周期向频率匹配算法模块输送一个数据。频率匹配算法模块是整个系统的核心,在实现该模块时,使用了两级流水线,大大加快了数据的处理速度。频率匹配算法模块的内部结构如图2所示,其中 reg1 和 reg2 用来保存sin(n)和cos(n)的值。

频率匹配算法模块的可综合RTL Verilog模型描述的代码保存在 freqmatch.v 文件中。另外,在设计的过程中,还编写了顶层测试模块文件 t_freqmatch.v,在该文件中,首先将 Matlab 生成的仿真数据(保存在 data.txt 中)读入到缓存器中,然后在每个时钟周期内向 freqmatch 模块发送一个数据。data.txt 文件的数据包含三个部分,前一部分为随机噪声,中间是频率为 500Hz 的正弦信号,后一部分是频率为 1000Hz 的正弦信号。在 freqmatch.v 文件中,将匹配信号的频率设为 500Hz。通过仿真,freqmatch 模块能够有效地将中间部分频率为 500Hz 的正弦信号提取出来。

结语

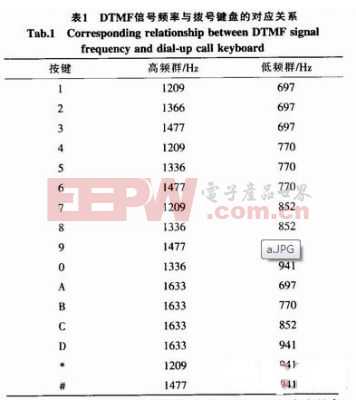

在设计的过程中,作者为该数字频率检测器编写了可综合的 RTL Verilog 模块,并通过了仿真和综合,其规模可以控制在合理的范围之内。另外,可以通过增加频率匹配中作相关运算的点数来提高频率检测器的精度。并且在设计中使用了一种改进的频率匹配算法,可以使硬件规模不会随着作相关运算的点数的增加而增大。由于频率匹配检测器与频率滤波器很相似,因此在这里借用频率滤波器的参数来描述频率检测器,表1和表2给出了根据频率匹配原理已经实现的几种频率检测器的参数(表中的通带指以该匹配频率进行检测时所能检测出的频率段)。

最后,需要指出的是本文所讨论的频率检测器与频率滤波器很相似,但它们有不同之处。使用理想频率检测器对信号进行处理时,能够将某一频率信号提取出来,但抹掉了原始信号中该频率信号振幅上的差异,即在输出信号中,该频率信号振幅是一个恒定值。而使用理想滤波器器对信号进行处理时,不仅能够将某段频率信号提取出来,而且不会改变该段频率信号的其它特性。■

参考文献

1 胡广书 编著. 数字信号处理——理论、算法和实现. 清华大学出版社,1997

2 王华 等编著. Matlab 在电信工程中的应用. 中国水利水电出版社,2001

3 戴逸民, 梁小雯, 裴小平 等编著. 基于 DSP 的现代电子系统设计.电子工业出版社,2002

评论