用PLD实现相位精确测量的研究

摘 要:本文介绍了一个采用PLD,利用MAX+PLUSⅡ和 EWB等开发工具,完成了功率因数精确测量的设计。其核心芯片是Altera公司ACEX 1K系列的EP1K10TC144-3。

关键词:可编程逻辑器件;MAX+PLUSⅡ;功率因数

引言

在电力系统中,由于负载均为感性,网上电流和电压之间存在相位差,影响供电效率。因此,减少无功功率,提高功率因数,事在必行。目前一般是采用并联电力电容的方法来提高功率因数,但如果并联太多电容器,电流就会超前电压,所以,准确地测量相位时间差对提高功率因数是致关重要的,本设计就是基于上述原因提出的。考虑到PLD集成度高、修改逻辑设计方便等优点,本设计采用PLD来实现。

PLD相位精确测量的

设计方案

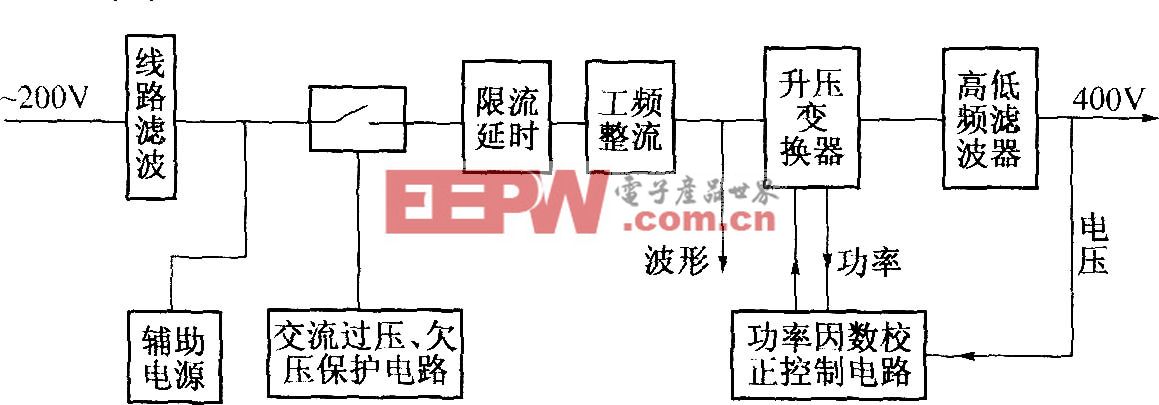

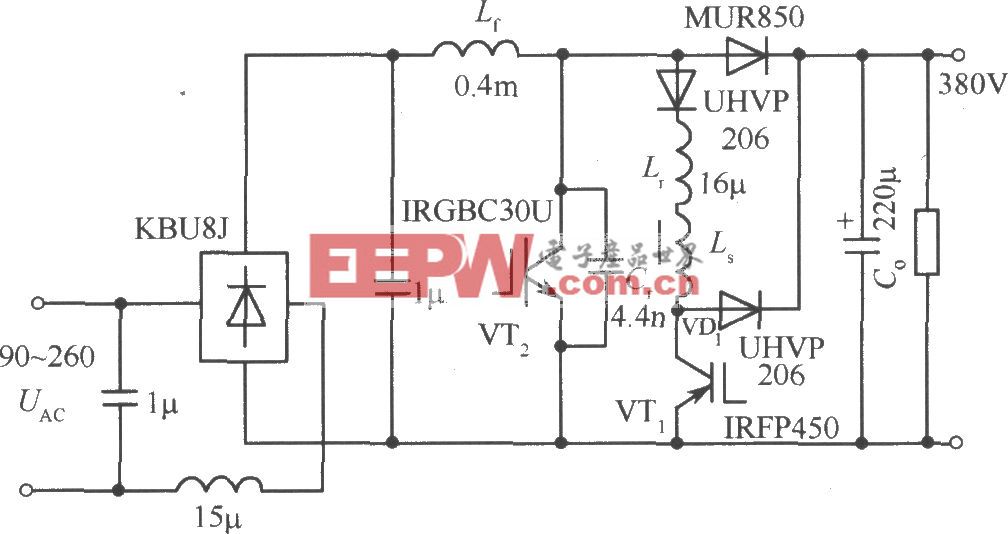

在电网上,电流和电压均为50Hz的正弦波,经放大整形后,以电流为时间基准,其波形如图1所示。

在 波形中,正脉冲宽度就是所要测量的I和V相位时间差ΔT。由于电网频率较低,采用单周期内测量相位时间差的方式,在检测中要考虑电压滞后和超前两种情况。PLD相位检测器原理框图如图2所示。

波形中,正脉冲宽度就是所要测量的I和V相位时间差ΔT。由于电网频率较低,采用单周期内测量相位时间差的方式,在检测中要考虑电压滞后和超前两种情况。PLD相位检测器原理框图如图2所示。

把 波形中的正脉冲作为门控信号,控制闸门的启闭,将标准(晶振)时间信号作为计数脉冲,实现I和V相位时间差ΔT的测量。从分频器输出的标准信号周期可设置为10-6s,在闸门开通时间,通过计数器对被测量

波形中的正脉冲作为门控信号,控制闸门的启闭,将标准(晶振)时间信号作为计数脉冲,实现I和V相位时间差ΔT的测量。从分频器输出的标准信号周期可设置为10-6s,在闸门开通时间,通过计数器对被测量 波形的正脉冲宽计数。控制电路通过自动和手动方式控制计数器和锁存器,最后通过译码显示电路显示电流与电压相位差的时间。

波形的正脉冲宽计数。控制电路通过自动和手动方式控制计数器和锁存器,最后通过译码显示电路显示电流与电压相位差的时间。

图1 I、V、 波形图

波形图

图2 PLD功率因数检测器原理框图

图3 弹跳消除电路

图4 控制电路

PLD的相位检测器设计过程

信号的输入及整形

由于电压、电流信号都是50Hz的正弦波信号,为此,本设计把输入信号先经过7414变成方波后再异或,在设计中,经过移相后,作为两路输入信号(I和V)。

若信号源不稳定,则有时会存在峰刺的干扰,使得相位差不稳定,显示数据不正确。因此,必须在信号输入前加入消除峰刺干扰的电路。只要适当选取时钟信号,就能消除峰刺。

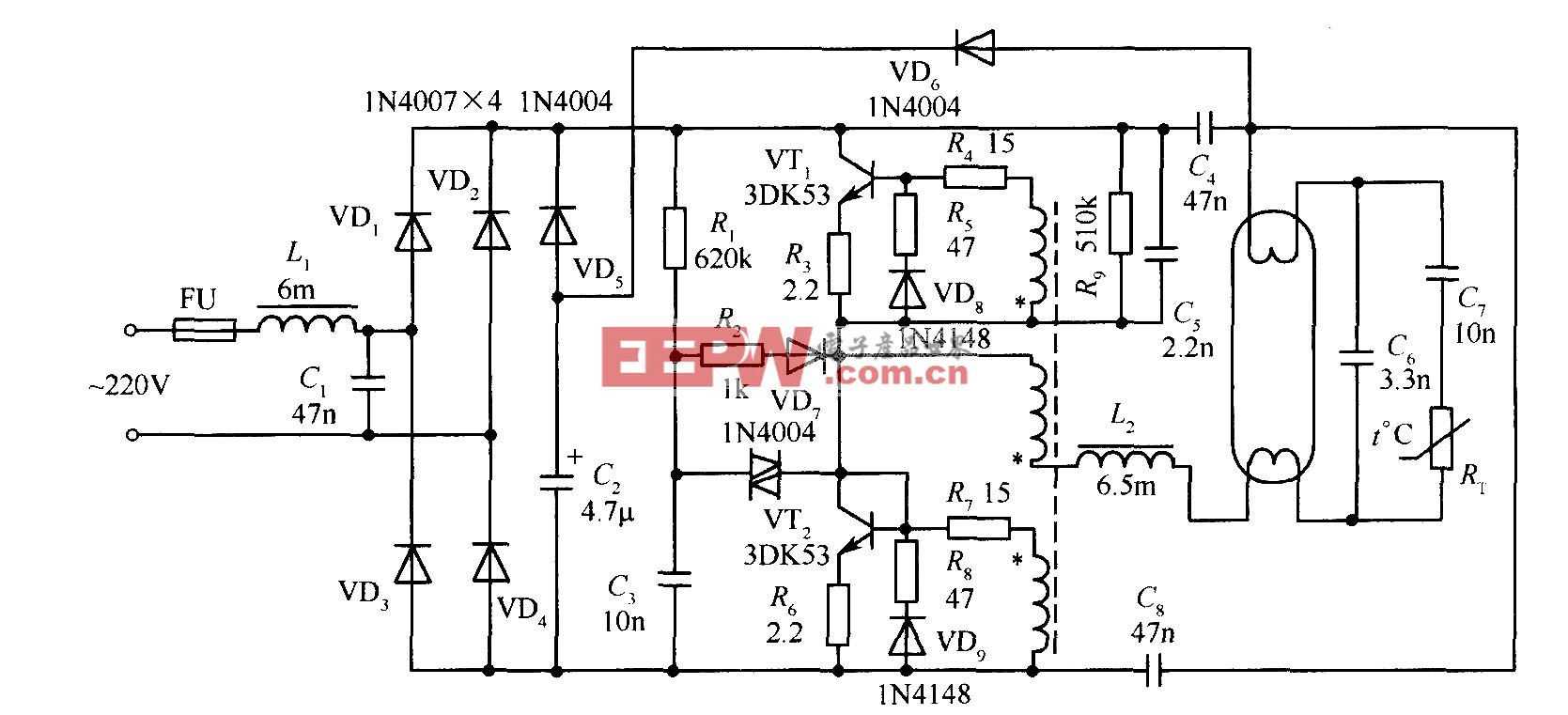

弹跳消除电路的设计

一般按键的弹跳现象指在按键信号稳定前后会出现一些不该存在的噪声,如果将这样的信号直接输入计数器电路,将可能导致误计数。

为了消除弹跳的信号现象,在设计中采取了如图3所示的电路。做法是先将按键的信号引至KEY脚,其中CP是电路的时钟脉冲信号(应视为取样信号,约为8ms左右)。KEY信号经过两级的D触发器延迟后,再用RS触发器作处理。

计数和显示电路设计

此电路用了4块74160十进制同步、可预置位的计数器,它具有内部先行进位的功能,可用于高速计数系统。其8位寄存器具有专为驱动大电容,或相对低阻抗而设计的图腾柱三态输出。

控制电路

由于电压和电流均为50Hz的正弦波信号,它们的异或信号频率为100Hz,如果每个周期都测量并显示的话,观察者将看不清楚所显示的数据。所以必须把输入信号分频,测出分频后的信号相位差,再由数学关系算出原信号的相位差;或者在测量并显示另一个周期内两信号的相位差后,延迟几秒钟,然后再测量并显示另一个周期内两信号的相位差。下面三种方案均能实现。

分频

原输入信号经整形(变成方波)后,再经过“弹跳消除电路”,变为频率为50Hz的方波信号, 为了观察者能看清楚所显示的数据,必须分频为0.1~1Hz的方波信号。为此,本设计把两路信号都经过两片74393分频,调整分频倍数,使其频率符合要求;考虑到此时时钟频率过大,四位十进制数不能完全显示(大概需要五位),所以时钟信号也必须经过分频,把分频后的信号作为新的全局时钟信号。

提取一个或几个周期

由于相位差信号为连续的100Hz的周期信号,这样,可以采用定时抽样的方法,每隔几秒钟的时间就测量并显示一个周期内的相位差或几个周期内相位差的总和。

提取一个周期

利用三片74161作为延时电路,并利用74161的进位时间就是一个相位差信号周期的特点提取一个周期的相位差信号。控制电路如图4所示。K1为手动控制按键,K2为自动控制按键,1脚为相位差信号,Clk为分频后的全局时钟信号(计数脉冲),2脚接计数器74160的时钟输入端,3脚接计数器的清零控制端,4脚接寄存器的输入允许端。把1脚的相位差信号作为74161的时钟信号。为了起到延迟的作用,本设计把“011111111111”和“100000000000”之间的一个相位差信号的周期提出来,这样就得到一个周期为4096个相位差信号周期,正脉宽为1个相位差信号周期的脉冲信号(称为脉冲1),再把这个信号和相位差信号相与,新的脉冲信号的周期仍然是4096个相位差信号周期,但正脉宽等于1个相位差信号的正脉宽(称为脉冲2)。把这个信号作为闸门信号去控制计数闸门,即与计数脉冲一起通过一个与门,这样就实现了每4096个相位差信号周期时间(大约8秒钟时间)测量并显示一个相位差信号。把这个脉冲分频后接上一个D触发器,就得到一个周期不变、占空比为50%的方波信号,利用这个信号去控制计数器74160的清零端,这样就实现了每周期计数一次、清零一次的功能(数据不会累加到下一个周期)。利用脉冲1去控制寄存器74373的输入允许端,只有当计数器处于计数状态时才允许输入,把得到的数据保存并显示;当计数器处于清零状态时不允许输入,寄存器保存原来的数据并显示。

按键K1,K2都能产生一个单脉冲,经过D触发器以后就会成为一个长时间的高电平,K2后面的信号控制着计数闸门的后一级,即只有当K2按下一次后,计数电路才能开始工作,这样就实现了自动计数。K1后的D触发器清零端被脉冲1控制着,K1每按下一次,只能产生一个时间为1个脉冲周期的高电平,即每按下一次只能计数一次,这样就实现了手动控制。

误差分析

设计中的误差主要来自于两个方面:

(1)信号经过一个电路器件会有10ns的延时。本设计中,相位差信号经过控制电路后产生了大约100ns的延时,延时后的信号再与原来的相位差信号相与就会使相位差减少100ns。不过这个误差比较小,可以忽略。

(2)信号源不稳定及晶振质量的好坏是本设计中最主要的误差。解决的办法是采用紧密稳压电源及质量较好的晶振。■

参考文献

1 《EDA技术及应用教程》,四川大学出版社

2 刘笃仁,杨万海.《在系统可编程技术及其器件原理与应用》,西安电子科技大学出版社

3 王毓银.《脉冲与数字电路》,高等教育出版社

4 杨晖,张凤言.《大规模可编程逻辑器件与数字电路设计》,北京航空航天大学出版社

5 《现代数字系统设计与在系统编程技术》,东南大学无线电工程系

评论