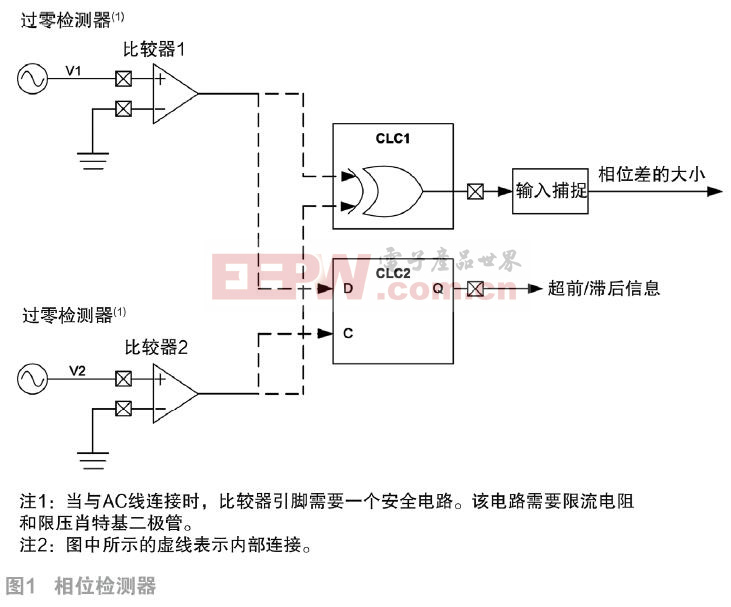

PLD在DRFM中的应用

摘 要: 本文提出一种基于PLD实现的DRFM(数字射频存储器)设计新方法,并进行PLD软件设计。DRFM在电子对抗系统中将雷达信号下变频后的信号进行采样存储,再延时转发出去,从而实现距离上的欺骗干扰。利用PLD控制不仅使其优越性能得到充分发挥,还使得电路的设计简单、灵活。

关键词: PLD;DRFM;距离欺骗

引言

由于现代雷达采用多种先进技术反干扰,如果欺骗信号不具有相参性就很容易被敌方雷达识别,并被作为反跟踪和打击的目标。在一般的情况下,认为DRFM复制出的信号与雷达回波信号相参,所以利用它能够对现代雷达进行欺骗。

欺骗的实现过程是这样的:首先DRFM对输入的信号进行采样存储,经过一段延时后,将存储的信号输出。这样可在输入和输出之间得到所需要的延时。由于输出的信号相比较,输入信号没有改变,只是时间上拖后,所以当这种延时应用在雷达对抗中,就可以产生了比真实目标远的假目标,即距离欺骗。

DRFM一般包括以下几个部分:控制器、ADC、DAC和存储器。在本设计中应用Altera公司的MAX3000A系列器件进行DRFM实现。

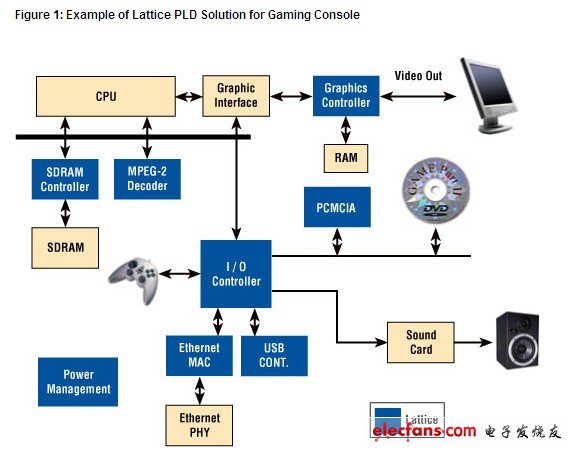

图1 宏单元中的乘积项

图2 PLD实现DRFM框图

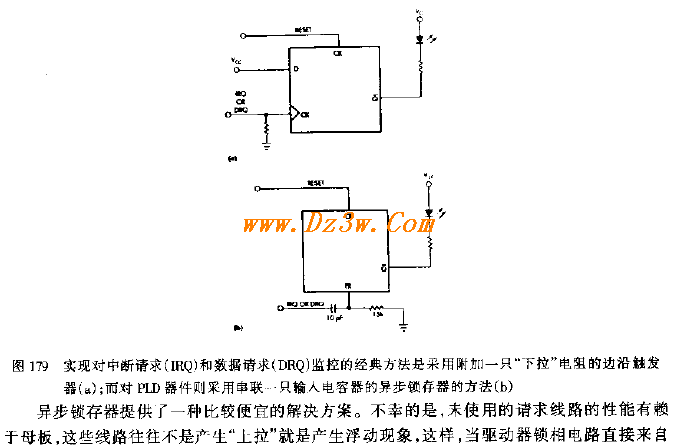

图3 四路存储时钟时序图

图4 读写时钟实现逻辑图

MAX3000A的结构和性能分析

MAX3000A系列功耗低、逻辑功能强,相比较同类型的MAX7000A系列,其性价比显得更高。其所包含的MAX3064的一些结构特征参数为:可使用门数:1250个;宏单元:64个;逻辑阵列块(LAB):4个;最大可使用输入输出管脚数:64个;最大工作时钟频率:222.2MHz。

其宏单元的基本结构是一个乘积项(如图1),每个逻辑阵列块都包含16个宏单元,通过这种结构和其扩展可以实现更为复杂的逻辑功能。

此外,每个宏单元通过一个可编程寄存器,对时钟和控制信号进行统一的管理,从而可以稳定地实现高速逻辑运算。

系统结构

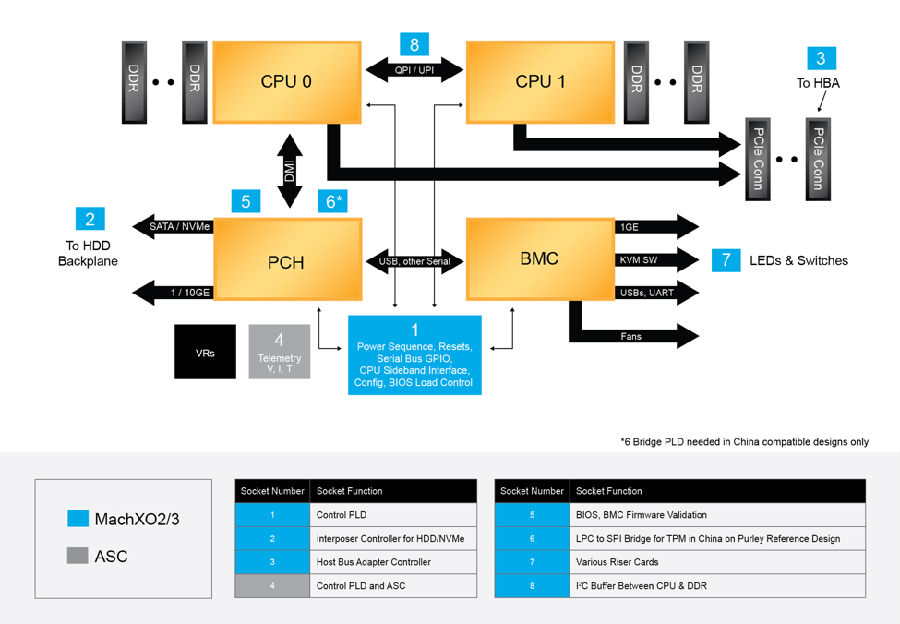

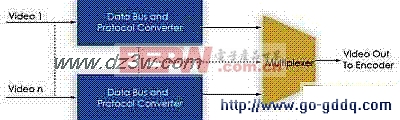

DRFM系统的构成如图2所示,它由PLD、ADC(8位)、FIFO、DAC(8位)和单片机构成。其中单片机负责与外界通信,确定是否有信号输入。

工作过程如下:首先DRFM将接收机接收的信号下变频,经过ADC进行模数变换形成高速数据流,然后这些高速数据流被分成四路或者多路相对低速的数据流进行存储,接着在PLD的控制下,再利用和FIFO写时钟相同的时钟读出FIFO中存储的数据,最后四路数据经由合成器和DAC传输给上变频器发射出去。

图5 PLD实现延时流程图

图6 延时设计逻辑框图

图7 PLD 延时实现输出波形图

图8 延时模块相关应用简图

PLD的编程实现

对于整个电路来说,关键是工作时钟和延时功能的实现。

为了满足系统的工作带宽,通常会采用很高的工作时钟(根据那奎斯特采样定律,采样时钟至少应为信号带宽的两倍)。但是,高时钟存储会增加电路设计的成本。所以通常采用高采低存技术来降低成本,即将采样的数据流分成多路数据流进行存储。举例来说,采样速率为400MHz,当分成四路进行存储后,每一路的存储速率为100MHz。但是,将数据流分成多路进行存储,其存储时钟沿又很难保证对应关系(四路时钟每路900相移),而利用PLD设计可以很好地解决这些问题。

时钟实现

对于DRFM来说,多路FIFO写、读时钟直接关系到数据是否能够被有效地写入和读出,如果时钟处理不当,整个系统就不能有效地工作。利用单独的D触发器和与或门逻辑器件组合,也可以实现四路时钟,但稳定性不能保证。而利用PLD实现四路时钟,可以相对容易地实现比较稳定的四路时钟,且每路时钟沿都能保证得很好。如图3所示,采样时钟二分频后的时钟信号用作PLD的全局工作时钟,通过一定的逻辑最终实现四路时钟信号。

在信号合成中也利用到图3中的四路存储时钟,即用四路时钟将数据读出后,同时让四路时钟作为选通器件使能信号(使能信号高时为有效输出,低时输出低电平),这样在采样时钟的每一个周期内只有一个数据有效,并且四路输出叠加后信号与有效输出的一路相同,从而完成了数据的合成。

图3中,如果每一路FIFO能够实现最大的工作时钟是100MHz,当采用四路并行工作后,采样时钟就可以达到400MHz,比单路存储工作其时钟提高四倍。

为了实现上述对应的时钟关系,采用图4的设计。

其中CIN是采样时钟二分频后时钟信号。其被分成两路反向时钟后,经过一次分频,再将输出时钟进行一定的逻辑调整,就得到了四路时钟。

采用正交采样技术,可以将系统的时钟扩展一倍。如果将正交采样技术和分路存储技术(假设四路存储)结合到一起,在不考虑系统体积的因素下,理论上可以将整个系统时钟相对于单路存储扩展8倍。

延时的实现

DRFM的距离欺骗是通过FIFO读使能和写使能之间的延时来实现的,其原理如下:通过单片机给定的中断信号确定是否有信号输入。当确定有时,将信号采样存储,同时启动内部计数器工作。当计数器计数到一定值(其值可以通过单片机给定,也可以通过PLD内部得到)时,使FIFO读使能有效,将数据读出交由DA变换,从而完成一定延时功能。此延时值根据模拟不同的运动方式(匀速运动、加速运动)应分别满足下面的关系:

当前一次延时操作完成后,PLD从单片机将另一延时值读入,或者自动产生另一延时值,并且将读写使能都置为无效(FIFO为空时,读自动无效),等待下一次信号的输入。

为了确保信号数据全部存储而不被丢失,除了使FIFO存储容量满足一定要求,还应使得写使能有效期内,存储的数据不能超过存储器的存储深度,以避免数据溢出。

为了使得延时值不会超过雷达所能探测的最大距离,计数延时的最大值也应该满足一定的要求。

设计流程图如图5所示。在设计中,采用的方式是内部自发产生延时值。其中cin1[7..0]为循环计数值,gclk为全局工作时钟,rsin为外部中断信号,ren1、wen1 为FIFO读写使能信号,低有效。其设计逻辑图如图6所示。

图6包括三个模块:add模块、yanshi3模块和2xuan1模块。其中add模块循环实现加功能,2xuan1模块确定延时值不超过最大值,yanshi3模块则根据add模块的结果进行延时。图7是最后的仿真结果(部分)。

gclk是全局输入时钟信号。rsin是信号输入确定,高电平表示有信号输入,高电平所持续时间的大小相对于信号的长短。empty由FIFO给定,当FIFO读出所有的数据时,自动置empty为高,并使得读无效;当有数据写入时,这个值赋为低。wen1和ren1为FIFO的读、写使能信号,低有效。

从图7可以看出,ren1每一次有效都要比wen1滞后一段时间这个时间是由cin1[7..0]的值确定的,并且cin1[7..0]能够根据需要改变。

相关应用

利用这种电路和延时线的结合,可以产生任意组合的延时(如图8所示)。

DRFM通常可以实现ms到ms级的延时,而延时线可以实现ps到ns级的延时。这样就可以通过DRFM粗延时,延时线微延时就可以实现各种宽范围,高精度的延时。其输入信号的带宽由DRFM的采样频率决定。

结语

基于PLD的DRFM设计新方法,通过采用四路并行时钟进行数据分流,从而在不提高存储时钟的前提下,提高了整个系统的工作时钟;并且通过逻辑设计能够很容易地实现精确的延时。■

参考文献

1 MAX3000A datasheet: MAX 3000A Programmable Logic Device Family.2002

2 周国富.数字射频存储技术.现代军事.1990(5)

3 苟仲文.200MHz数字射频存储器.电子对抗技术.1998(12)

4 林象平.雷达对抗原理.西安:西北电讯工程学院出版社.1986

评论