驱动器UCC27201上电时刻HO引脚误脉冲的分析及解决

在隔离 DC/DC 电源中经常会使用到带浮地功能的双通道驱动器 UCC27201。实际应用发现,某些场景中,其HO 引脚会在上电时刻产生误脉冲。该误脉冲导致系统有开机异常的风险。本文通过实际仿真和电路原理分析,详细介绍了误脉冲产生的机理,随后提供了两个针对该误脉冲的解决方案,并给予了详细解释。

本文引用地址:https://www.eepw.com.cn/article/282646.htm1、隔离电源系统设计

某隔离电源系统完成 DC/DC 的转换,采用全桥拓扑,输出电压为 12V。其中,全桥的原边侧驱动器就采用了UCC27201,共计两颗。

1.1 隔离电源系统简述

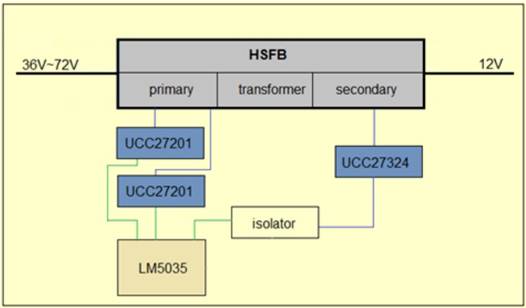

该隔离电源系统完成宽范围输入电压(36V~72V)到 12V 的转换,输出功率 350W。系统采用带同步整流功能的硬开关全桥拓扑(HSFB)。图 1 所示的是该系统的方框图,包含有主控芯片 LM5035,置于原边侧的驱动器UCC27201,置于副边侧的驱动器 UCC27324 和隔离器等器件。

图 1:隔离电源系统框图

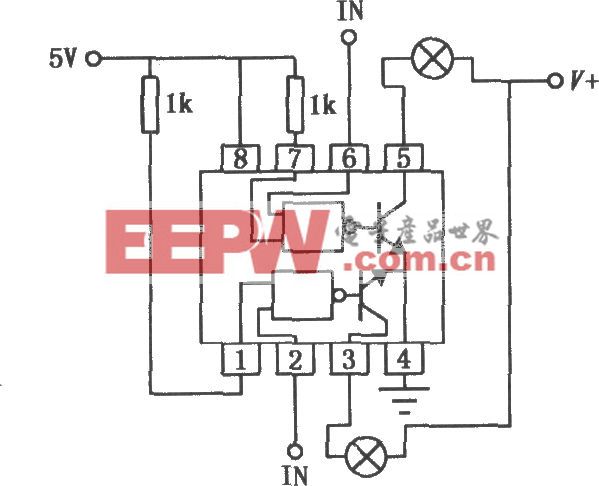

1.2 UCC27201 的应用

UCC27201 是带有浮地功能的 MOSFET 驱动器,具有高端输出和低端输出两个通道,可以应用于 BUCK,半桥和全桥等拓扑。该芯片引脚的描述如下:

● VDD (Pin1) :供电引脚,范围是 8V~17V,典型值为 12V;

● VSS (Pin7) :芯片地引脚;

● HI, LI (Pin5, Pin6) :高端驱动输入和低端驱动输入;

● HO, LO (Pin3, Pin8) :高端驱动输出和低端驱动输出;

● HB, HS (pin2, pin4) :浮地供电和浮地引脚,用于高端驱动供电;

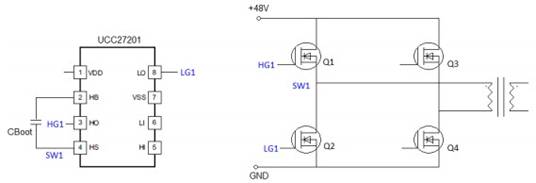

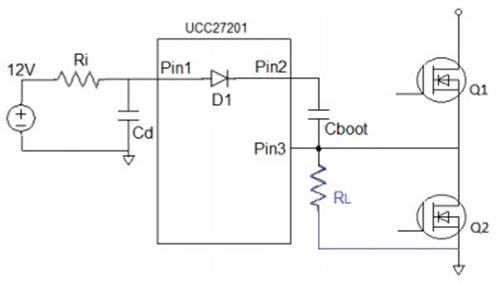

如图 2,在本电源系统中,一颗 UCC27201 的两路输出驱动全桥同一侧桥臂的两个 MOSFET,主要连接网络标示如蓝色字体。另一颗 UCC27201 的两路输出则是驱动全桥的另一侧桥臂。

图 2:驱动器 UCC27201 的实际应用

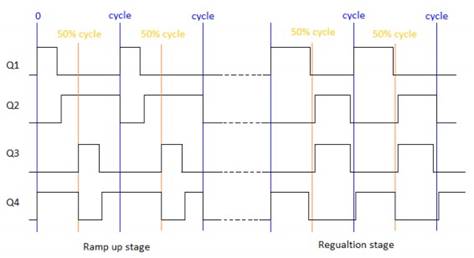

采用上述应用电路的实际驱动信号见图 3,包括了软启动和正常运行等两个阶段。

在软启动阶段,标示为 Q1 的 MOSFET 的驱动信号占空比远小于 50%,而 Q2 的驱动信号占空比则是超过了50%,与 Q1 的驱动信号占空比保持为互补关系。Q3 和 Q4 驱动信号的关系同上。

在正常运行阶段,Q1~Q4 的驱动信号占空比全部都接近 50%。相互之间的关系如图 3 所示,即 Q1 和 Q2 保持互补,Q3 和 Q4 保持互补。

图 3:全桥驱动信号

2、UCC27201 HO 引脚的误脉冲及根因分析

实际应用中,由于不同的 UCC27201 的供电电压设计有差异,当其 Cboot 电容充电过快时,HO 引脚会出现误脉冲。该误脉冲的根因是 Cboot 过快的上电电压耦合到了 HO 引脚,同时过快的上电速率导致芯片内部对 HO 管脚下拉的 MOSFET 不能及时导通,最终造成了 HO 引脚输出误脉冲。

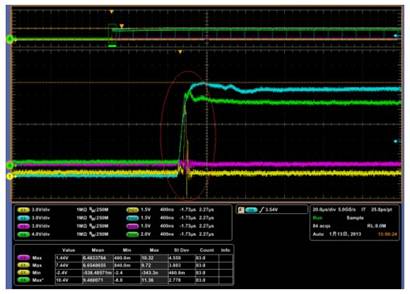

2.1 HO 引脚的误脉冲

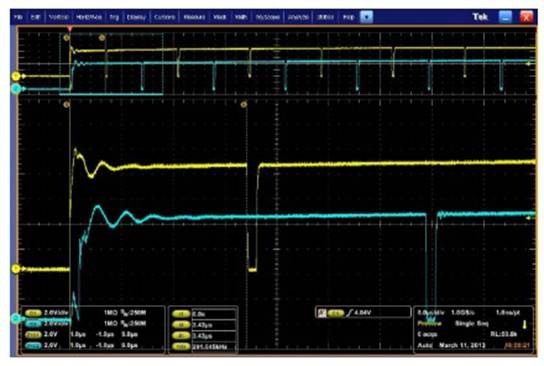

实际测试上述电源系统时发现,开机时 UCC27201 的 HO 引脚有误脉冲,如图 4 (CH1 为 HO;CH4 为 HB 与HS 的差分电压,亦即 Cboot 电容两端的电压;CH2 为 LO;CH3 可忽略)。该误脉冲幅度最大可超过 7V,与 LO交叠后会造成全桥高端 MOSFET 和低端 MOSFET 的共通,进而导致系统开机存在风险。

图 4:HO 引脚的误脉冲

2.2 HO 引脚误脉冲的根因分析

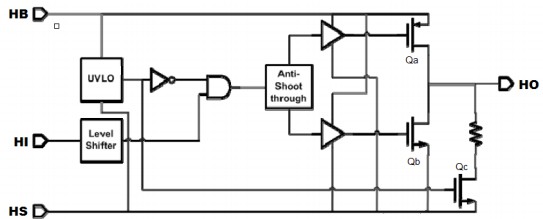

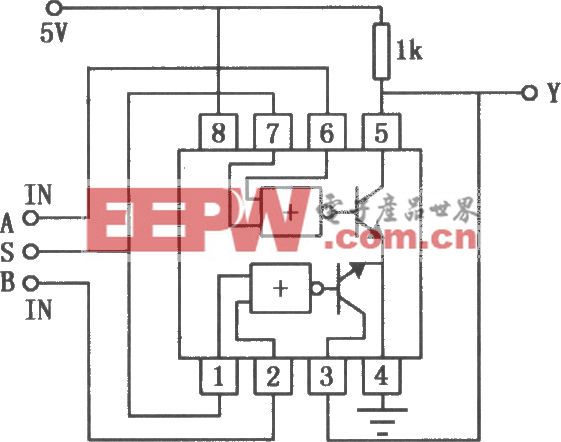

图 5 所示的是 UCC27201 内部与 HO 相关的电路。在 HB 与 HS 之间电压正常建立后,逻辑电路会依据 HI 电平的高或低而打开 Qa 或 Qb,从而实现 HO 高低电平的输出。Qc 是当 HB 与 HS 之间电压还处于欠压阶段时,用以导通以拉低 HO 引脚,确保在该阶段 HO 无输出。

图 5:HO 相关的内部电路

当 HB 与 HS 间电压还处于欠压阶段时,内部电路会产生高电平驱动信号以导通 Qc。但是,该高电平驱动信号的产生存在一定的延时;同时,Qc 设计用来被脉冲信号触发,而非电平信号触发。上述两个因素就造成,当 HB与 HS 间电压上升过快时 Qc 将不能及时导通。此时,如果 HO 被 HB 与 HS 间电压耦合出高电平后(其中一个耦合途径是通过 Qa 和 Qb 的结电容),因 Qc 还未导通,该耦合出的高电平将得以输出,最终形成了 HO 的误脉冲。

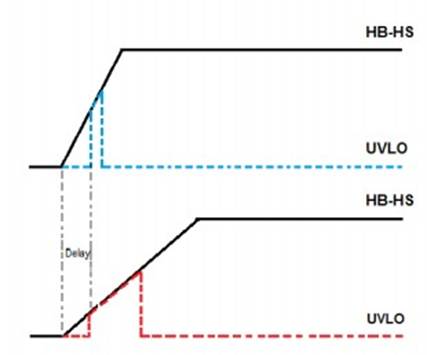

如果 HB 与 HS 间电压上升速率变缓,或者 HB 与 HS 间电压先得以预建立,Qc 的驱动信号(图 6 中的蓝色线和红色线)的高电平脉冲将会变宽,这就能保证 Qc 导通,误脉冲就会被消除。

下文就围绕 HB 与 HS 间电压的上升斜率和预建立这两个方向来讨论,以解决 HO 的误脉冲问题。

图 6: HB 与 HS 电压斜率不同的影响

3、解决措施之增大 Cboot 电容

在相同充电速率条件下,增大 Cboot 电容可以将 HB 与 HS 之间的电压上升斜率变缓,以得到足够宽的高电平信号并使 Qc 导通。

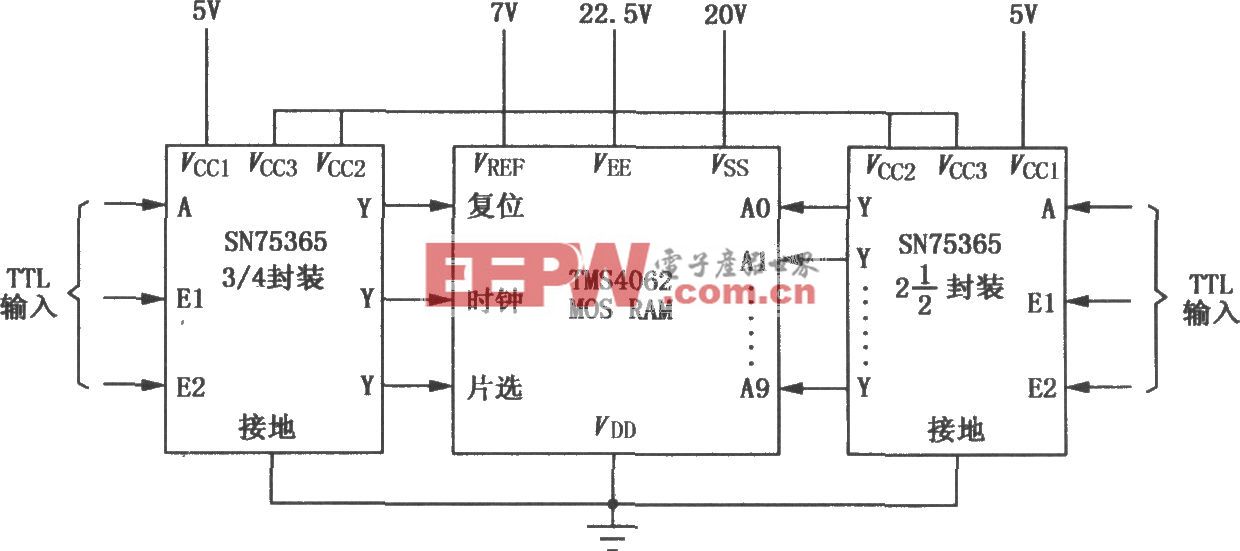

3.1 Cboot 充电过程分析

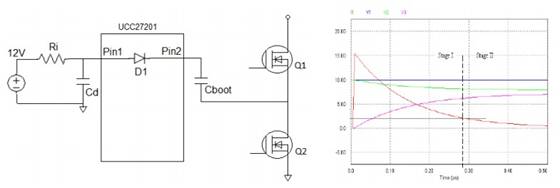

如图 7 所示,UCC27201 内部有二极管(D1)连接 Pin1 (VDD)和 Pin2(HB)。在 Pin1 的外部连接有供电网络(电压为 12V),电容 Cd(1uF)和串联电阻 Ri(10ohm);在 Pin2 则接有 Cboot 电容。Cboot 电容的充电主要是通过 D1 这条路径完成的。

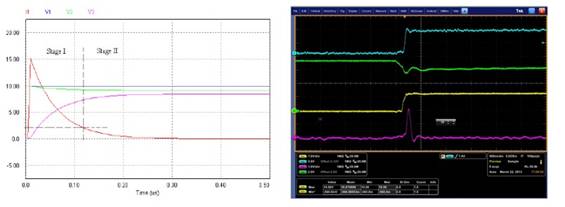

经过仿真分析(如图 8)知,Cboot 的充电主要包含如下两个阶段:

●阶段一:电容 Cd 通过 D1 给 Cboot 充电。充电电流如图 8 中的红色线所示,先是急剧上升到最大,然后缓慢下降。同时,电容 Cd 的电压(绿色线)逐渐下降,电容 Cboot 的电压(粉色线)逐渐上升。当 Cd 与 Cboot的压差减小为约 0.65V(二极管 D1 的正向导通压降)时,第一阶段结束。

●阶段二:12V 供电电压给 Cd 和 Cboot 充电。受限于 Ri,充电电流将小于 1.2A (12V/10ohm)。

图 8 中的仿真结果是基于 Cboot 为 300nF,图 9 的仿真结果则是基于 Cboot 为 100nF。对比二者知,修改 Cboot电容容量所带来的主要影响是第一个充电阶段的持续时间,分别约为 280ns 和 120ns。下节会分析第一阶段持续时间不同可能会带来的风险。

图 10 给出的是实测波形,其中 CH1 是 LO 的波形;CH2 是 HB-HS 的波形;CH3 是 HO 的波形,CH4 是 VDD的电压波形。可以看到,在 UCC27201 上电后,VDD 电压快速下降,然后又缓慢上升,这与仿真结果一致。

图 7:Cboot 电容充电电路 图 8:Cboot 为 300nF 时的仿真结果

图 9:Cboot 为 100nF 时的仿真结果 图 10:充电过程的实测波形

3.2 增大 Cboot 电容的风险分析

在 UCC27201 的实际应用中,需要注意内部二极管 D1 的反向恢复应力。

当 LO 的输出 由高变低后,HS 电压会升高,HB 电压同样也会升高,此时内部二极管将承受反压,并承受随后出现的反向恢复应力。如果反向恢复应力出现之前时刻的二极管正向导通电流超出额定范围,反向恢复应力则会过大而导致二极管失效。UCC27201 要求内部二极管承受反向恢复应力前的正向导通电流在 2A 以下。

在该电源系统中,将 Cboot 修改为 300nF 后,二极管正向电流在约 280ns 后降低到 2A。而在开机的第一个周期内,下管的持续时间超过了 3us(如图 11,CH1 和 CH2 是全桥两个下管的驱动信号),即 3us 之后内部二极管才会有反向恢复应力,由于此时正向导通电流已经远低于 2A,二极管无可靠性风险。因此,修改 Cboot 容值到 300nF后二极管不会有失效风险。

图 11:开机时刻全桥下管的驱动波形

4、解决措施之 Cboot 电容预充电

给 Cboot 电容预充电,可以提前产生驱动信号以确保内部 Qc 导通。当系统发波后,LO 变高会产生充电路径而使 Cboot 快速充电,但由于此时内部 Qc 已经导通,HO 将不会产生误脉冲。

4.1 预充电电路

如图 12 所示,增加一颗电阻 RL后即可形成预充电电路。当 UCC27201 的 12V 建立后,在系统未发波前,12V电压可以通过路径 Ri->D1->Cboot->RL给 Cboot 充电。

经仿真知,当对 Cboot 电容预充电至 1V 左右,内部 Qc 就会导通。于是,随后的快速充电将不会再在 HO 引脚产生误脉冲。根据 12V 建立到系统发波之间的延时时间,可以计算合适的 RL值,以保证 Cboot 预充电至 1V 以上。

图 12:Cboot 电容的预充电电路

4.2 新增电阻的阻值计算

假设延时时间为 1ms,根据如下 RC 充电公式,可知 RL 约为 114Kohm。

12V x [1 – exp(-1ms / RL*Cboot )] = 1.0V

考虑到系统正常运行后,全桥上管导通时,电阻 RL 存在一定的损耗。最恶劣条件下(高压输入)的损耗计算如下:0.5 x(72V*72V)/100K=0.026W

综上可知,实际应用中,可以选取阻值为 114K,封装为 0603 以上的电阻,只要延时时间不少于 1ms,就可以确保 HO 引脚无误脉冲输出。

5、总结

在 UCC27201 的实际使用中,如果 Cboot 电容充电速率过快,则会在 HO 引脚产生误脉冲。通过对误脉冲产生机理的分析可知,通过增大 Cboot 电容的容量或者在 HS 引脚增加一颗连接到地的电阻,都可以有效的解决该问题,而且上述两个方法都不会对系统带来额外的可靠性风险。

但需要注意的是,在采用上述两种方案前都需要仔细评估,以确定当前应用条件下,上述方案不会带来风险。可以邀请 TI 工程师共同参与该评估过程。

6、参考资料

1. UCC27201 datasheet, Texas Instruments Inc., 2008

2. LM5035 datasheet, Texas Instruments Inc., 2013

评论