D触发器原理之低调的真相

导读:触发器又称为双稳态多谐振荡器,是一种可以存储电路状态的电子元件,广泛用于运算器、计算器、存储器中。最简单的触发器便是RS触发器了,相信大家都有所了解,今天在此基础上,我们一起来八一八D触发器原理的真相。

本文引用地址:https://www.eepw.com.cn/article/269468.htm一、D触发器原理- -简介

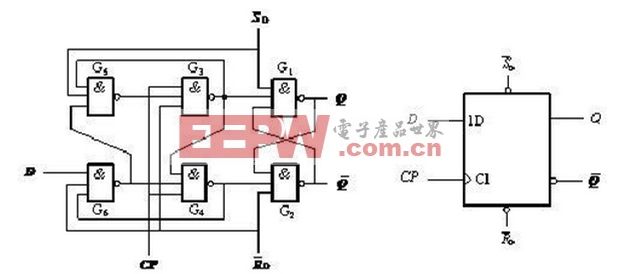

D触发器(data flip-flop)也称为维持-阻塞边沿D触发器,由六个与非门组成,其电路图及其逻辑符号如下图所示。其中G1和G2构成基本的RS触发器,G3和G4构成时钟控制电路,G5和G6组成数据输入电路。由于 分别为复位端和置位端,在分析D触发器工作原理时均视为高电平,以保证不影响电路工作。

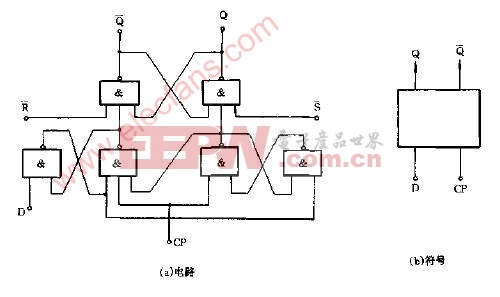

二、D触发器原理- -钟控D触发器

在分析维持-阻塞边沿D触发器的工作原理之前,让我们先来看看 的复位功能 的置位功能是如何实现的吧。

电路中的 端分别完成复位功能和置位功能,均为低电平有效,即 时,不论输入数据D处于什么状态,其输出端都为 ;而当 时,不论输入数据D处于什么状态,其输出端都为 。具体工作原理如下:

(1)当 时,G2输出端为1,即 ;与此同时, 的低电平到达G6的输入端,使得G6输出端为1,G5输出端为0,G3输出端为1,此时G1的三个输入都为高电平,从而导致其输出端为低电平,即Q=0。完成了触发器复位的功能。

(2)当 时,G1的输出端为1,即Q=1;与此同时, 的低电平到达G5的输入端,使得G5输出端为1,当CP=1时,G3输出端为0,G4输出端为1,此时G2的三个输入都为高电平,从而导致其暑促段为低电平,即 。完成了触发器置位的功能。

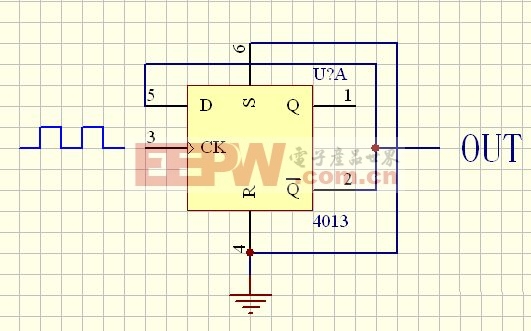

三、D触发器原理- -边沿D触发器

根据以上对钟控触发器的分析可知, 的复位功能和 的置位功能与CP信号无关,均为低电平时有效,而当 、 均为高电平时,输出端状态取决于输入端D,其工作原理如下:

(1)在D=0前提下,G6输出端为1。当CP=0时,G3、G4输出端都为1,G5输出端为0,使得G3输出端恒为1,保持不变;当CP由0变为1时,G3保持输出端为1,G4输出端变为0,从而导致 ,而G4输出端连接到G6的输入端,使得G6输出端恒为1,在改变D时也保持不变。故将G4到G6的连接线称为置0维持线,故将G3到G4的连接线称为置0阻塞线。

(2)在D=1前提下,当CP=0时,G3、G4输出端都为1,G6输出端为0,使得G4、G5输出端恒为1,保持不变;当CP由0变为1时,G3输出端变为0,从而导致 ,而G3的输出端连接到G5的输入端,使得G5输出端恒为1,在改变D时也保持不变。故将G3到G5的连接线称为置1维持线,G5到G6的连接线称为置1阻塞线。

根据以上分析可知,该边沿触发器的特性方程为 。由于采用了维持阻塞的结构,当时钟信号CP的上升沿到来时,将D的数据送到输出端,具有边沿触发的特性,而在CP信号上升沿之后,即使D的数据发生了改变,输出端也不会发生改变。

小编在这再为您奉上几篇关于D触发器原理的精美文章,敬请关注~~~

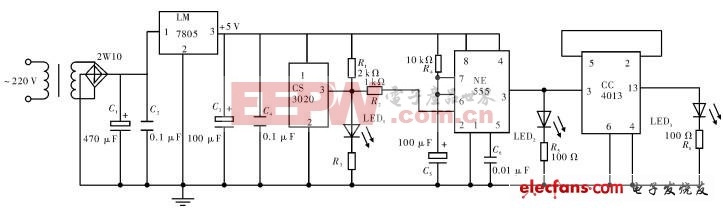

1、同步D触发器原理

电气符号相关文章:电气符号大全

评论