短波扩频猝发通信系统的DSP+FPGA设计方案

引言

短波通信是一种能进行远距离传输,而对电台的要求相对较低的通信系统。短波具有的远距离通信能力和电台具有的较高机动性等特点,使其在军事通信领域中具有重要的应用价值。然而,短波信道频带窄,传播特性不稳定,干扰严重,信号易被敌人截获、测向和干扰。一种有效的抗干扰措施就是将扩展频谱通信技术及猝发通信技术应用于短波通信中,进行短波超快速扩频猝发通信。随着现代通信技术的飞速发展,特别是扩频技术在第三代移动通信中的成功应用,为实现扩通信和猝发扩频数据传输奠定了技术基础。超大规模集成电路和高速信号处理器高效的处理能力和处理速度也为实现短波猝发扩频数据传输提供了良好的硬件平台。

本文首先给出了一种DS-QPSK短波扩频猝发通信的系统方案,着重对其中的同捕获技术进行了研究,采用滑动相关法来实现序列的同步,并运用Matlab工具对其进行了仿真。然后采用TMS320VC33、TMS320VC5509和ALTERA公司的Cyclone系列FPGA构建了硬件平台,给出了DSP+FPGA的混合硬件实现方案。

短波扩频猝发通信系统方案

系统构成

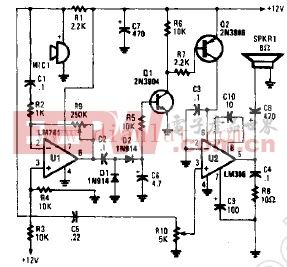

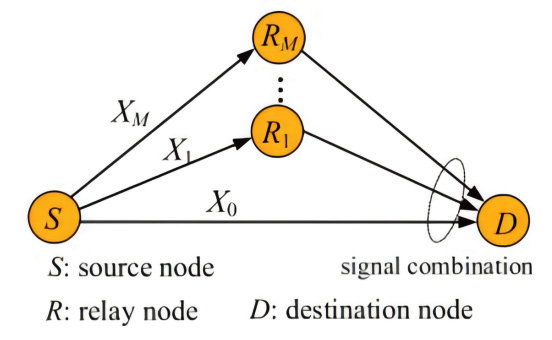

本系统采用了直接序列扩频技术来实现无线短波数据的发送和接收。具体实现是用32位的沃尔什序列对信息速率为2.4Kbps的数据进行直接序列扩频。在接收端利用扩频码的正交性对数据进行相关解扩,恢复出原始信息,并且由于QPSK调制技术抗噪声性能强,频谱利用率高,结构简单,所以这里采用它作为数据调制方式。数据传输采用超快速猝发通信方式,即每次通信的时隙限定在100ms左右,发送时隙随机分布,难以被捕获和干扰。每个时隙的数据发送前要发送一段同步头,用来完成扩频码的识别、扩频码的同步、帧同步和频差估计等任务,接收端根据同步头获得的信息对数据进行解扩恢复。为了改善性能,运用RAKE接收技术来接收数据,为了进一步提高系统的抗干扰能力,还对信息进行了1/2卷积编码,接收端采用Viterbi译码。系统的基本框图组成如图1所示,分成发射和接收两部分,分别完成数据的发送和接收功能。

系统同步方案

对于扩频系统,接收机要从接收信号中恢复发送的数据信息,必须对接收信号进行解扩。解扩的实现依靠本地产生与发送端相同的扩频序列,并且要求与接收信号扩频序列同步,这是扩频系统中非常重要的环节。

扩频序列的同步分为捕获和跟踪两个阶段。捕获阶段完成扩频序列的粗同步,将收、发端扩频序列的相位差限制在一个码片或更小的范围内;跟踪阶段实现收、发端扩频序列的精确同步,让本地参考信号精确跟踪接收信号的相位变化。如何可靠的实现扩频序列的快速捕获是影响系统性能的关键。常用的同步捕获方法有滑动相关法、同步头法、跳频同步法、发射参考信号法、匹配滤波器同步法等,而滑动相关法是一种最简单、最实用的捕获方法。本文采用的就是这种方法。确定信号捕获和完成码元同步,要求同时满足以下三个准则:①在连续4个接收码元中至少有3个与预定同步码的顺序相吻合;②接收到的单音功率谱峰值高过门限;③各单音出现峰值间隔连续且次序正确。

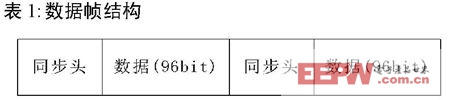

在本系统中,由于采用的是猝发通信形式,时隙较短,仅为100ms左右,因此可以认为信道短时平稳,发送数据的同步信息也可以一次确定,而且也可认为多径的每条路径上的时延也基本是恒定,因此只需由前导序列一次确定相关同步信息。由于发送的前导序列是双方约定好的正交码序列集,接收端利用码字的正交性,用本地序列与接收序列滑动相关,相关峰最大值所对应的位置即为同步点。如表1所示为发送数据帧结构。

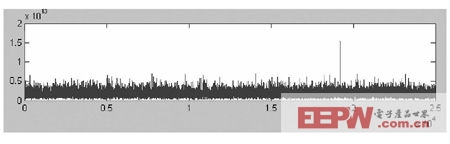

同步序列由48个32位Walsh序列构成,采用了级联编码。第一层编码为沃尔什序列加扰码。对于沃尔什序列来说,同步情况下的自相关和互相关性能很好。但是在非同步的情况下,沃尔什序列的正交性变差,相关函数有较大的旁瓣值,造成信号间的干扰。为减小旁瓣值,改善Walsh码的特性,用扰码乘以沃尔什序列,得到的新码作为前导序列的内码,则相关性能得到改善。第二层是对Walsh序列与48个相位组合的相乘,其中48个相位组合为 /4,3 /4,- /4,-3 /4的排列组合。经Matlab仿真取一组使所得到的相关峰较为理想,如图2所示。

数字通信相关文章:数字通信原理

通信相关文章:通信原理

评论