短波扩频猝发通信系统的DSP+FPGA设计方案

基于DSP+FPGA的硬件平台

本系统采用TI公司的高性能浮点数字信号处理器TMS320VC33和定点的TMS320VC5509两片DSP芯片作为系统的中央CPU,并采用ALTERA公司的Cyclone系列F

PGA设计出高速数字相关器,用于前端的信号同步与捕获,三个芯片协同工作,并以此为主体架构系统的整个硬件工作平台。

主要芯片介绍

TMS320VC33是TI公司推出的高性能浮点运算DSP芯片。由于其较高的性能价格比,使其应用较为广泛。它的结构允许它以定点的速率完成浮点操作,因此非常适合于做高速高精度的浮点运算,这一优点对于像短波信道快速估值等实时性精确度要求特别高的数字信号处理应用显得尤为重要。TMS320VC5509处理器是TI公司最新推出的高性能低功耗定点数字信号处理器TMS320C55x系列中的一员。TMS320C55x系列是在C54x系列的基础上发展起来的,能与C54x兼容,不仅增加了硬件资源,也优化了资源管理。

TMS320VC5509运行速度快,还可以进行多种并行操作,片内外设资源也比较丰富,与外围设备的连接很方便,所以非常适合用来作控制用。根据上述两种处理器的特点,综合考虑系统的设计要求,我们把TMS320VC5509作为系统的主处理器,而TMS320VC33作为其协处理器。

本文是采用Cyclone系列芯片来实现数字相关器对采样点值进行一次相关,将相关结果送给中央处理器DSP,进行下一步的同步和解扩等处理。ALTERA公司的Cyclone器件具有专用电路,可以实现双数据率(DDR)SDRAM和FCRAM接口。Cyclone器件最多有两个锁相环(PLL),共有六个输出和四种层次化结构,为复杂设计提供了强大的时钟管理电路。

系统硬件模型框图及概述

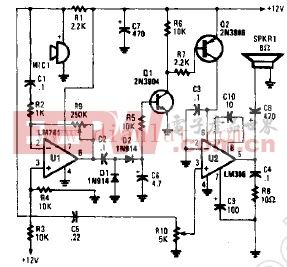

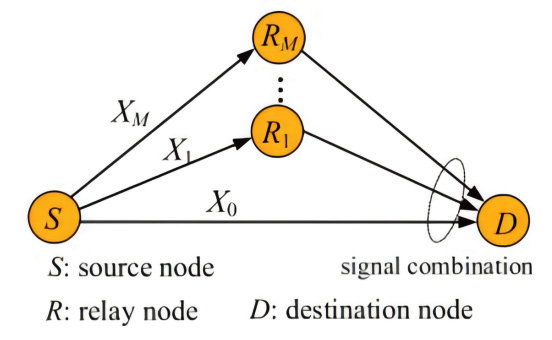

首先从电台接收过来的基带扩频信号是差分输入的,先经过一个1:1的隔离变压器变为单端输出,再经过运放将其抬高到直流电平以上,低通滤波后送到模数转换器AD7492进行采样处理,采样结果在FPGA中锁存,并在FPGA内部进行希尔伯特变换和相关处理。在一个样点间隔内,进行当前样点值的希尔伯特变换,同时并行地进行前一个样点的相关运算。将相关结果分成四个部分,锁存在对应的四个地址中,由TMS320VC5509分四次依次读取。由TMS320VC5509和TMS320VC33完成信号的捕获和码元的判决。将处理好的数据通过TMS320VC5509送到数模转换器TLV5619中进行数模转换,转换得到的模拟信号经过低通滤波和运放放大以后,再通过同样的一个1:1的隔离变压器变为差分输出送到扩频电台。如图3所示为系统的核心部分。

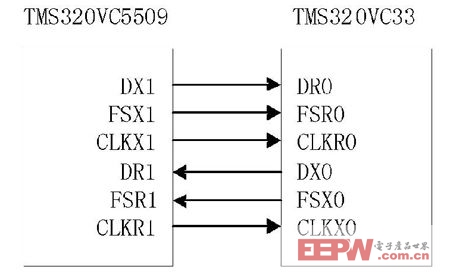

TMS320VC5509和TMS320VC33的互通

本方案采用的是用DSP串口来实现TMS320VC5509和TMS320VC33之间的通信。由于TMS320VC5509的多通道缓冲串口远比TMS320VC33的串行口功能强大,设置灵活,所以在设计的时候我们就考虑将TMS320VC5509的串口设为主方,TMS320VC33的串口设为从方,连接图如图4所示。

将TMS320VC5509内部采样速率发生器的输入参考时钟设置为CPU时钟,通过对CPU时钟的分频来得到串口移位时钟和帧同步信号,并由TMS320VC5509提供收发双方的移位时钟,而帧同步信号则由发送方提供。同时将TMS320VC33设置为标准模式、固定速率的工作方式,与TMS320VC5509的串口匹配。通过双方设置可以进行每帧16bit或32bit的传输。这样双方DSP可以通过握手,采用中断或查询方式来进行数据的高速收发,并且还可以灵活地对双方串口的工作方式进行改进。

下面给出TMS320VC5509多通道缓冲串口及TMS320VC33串行口通信的关键程序段。

TMS320V

C5509多通道缓冲串口初始化程序:

MOV #0x0000,PORT(#SPCR2_1) ;采用多通道缓冲模式

MOV #0x0000,PORT(#SPCR1_1)

MOV #0x0040,PORT(#RCR1_1) ;接收每帧1个阶段,每阶段1个字,字长

MOV #0X0001,PORT(#RCR2_1) ;16比特,不压扩,1比特延迟

MOV #0x0040,PORT(#XCR1_1) ;发送每帧1个阶段,每阶段1个字,字长

MOV #0X0001,PORT(#XCR2_1) ;16比特,不压扩,1比特延迟

MOV #0x0003,PORT(#SRGR1_1) ;脉宽1个clkr/x,clkr/x为4分频(最大)

MOV #0x200f,PORT(#SRGR2_1)

MOV #0x0B00,PORT(#PCR1) ; fsr设为输入

MOV #0x0040,PORT(#SPCR2_1) ;GRST=1,启动采样速率发生器

MOV #0x00c0,PORT(#SPCR2_1) ;FRST=1,启动帧同步

MOV #0x00c1,PORT(#SPCR2_1) ;XRST=1,启动发送器

MOV #0x0001,PORT(#SPCR1_1) ;RRST=1,启动接收器

TMS320VC33串行口初始化程序:

LDI @p0_addr,ar0 ;p0_addr=808040h 总体控制寄存器

LDI 331h,r1 ;FSX/DX 设定为输出 CLKX设定为输入

STI r1,*+ar0(2) ;FSX/DX/CLKX串口控制寄存器

LDI 111h,r1 ;FSR/DR/CLKR设定为输入

STI r1,*+ar0(3) ;FSR/DR/CLKR串口控制寄存器

LDI @p0_global,r1 ;00e940004h 固定速率 标准模式 16bit STI r1,*ar0

LDI @buff_rec,ar7 ;接收缓冲区

LDI 020h,ie ;CPU串行端口0接收中断启用

STIR1,*+AR0(8) ;AR0指向串行端口总体控制寄存器(00808040h)

结束语

现代通信技术和超大规模集成电路以及高速信号处理器的高速发展,使得短波猝发扩频通信在军事通信中极具潜力。本文给出了一种DS-QPSK短波扩频猝发通信的系统实现方案,并运用TMS320VC33、TMS320VC5509和ALTERA公司的Cyclone系列FPGA构建的硬件平台进行了DSP+FPGA的混合硬件实现,得到的系统性能已达到预期的要求,实现了数据的有效实时处理。

数字通信相关文章:数字通信原理

通信相关文章:通信原理

评论