利用芯片上时脉实现高性能全速测试

全速测试在大量新功能的协助下有了很大的改进,包括在测试模式期间使用芯片上产生的功能时脉。目前许多设计都工作在非常高的频率,并包含许多时脉。芯片上锁相环(PLL)是一种制作内部时脉的常见方法。通常伴随PLL的还有乘法器、除法器以及其它时脉控制电路。不需要过多的附加逻辑,就能充分发挥用于测试的这些功能时脉的优势。

大多数公司都会在设计进入布局阶段之前使用静态时序分析(STA)检查功能时序。作为STA过程的一部份,设计师可规定设计时序约束和时序例外。本文所述STA过程的输出是新思设计约束(SDC)文件,该文件包括了STA过程中其它工具需要的时序信息。

只要能正确地利用芯片上时脉,就能实现更高性能且更精密的的全速测试结果,但在实际过程中,必须注意到工具的选择、不同特征尺寸元所具有的固有特性及其可能带来的影响等,可能必须采取不同的相应措施来应对不同情况。由于目前芯片的几何尺寸正不断微缩小,缺陷与时序的关系将越来越密切,因此,在130nm以下的制程节点中,不应该完全依赖连续故障模型。本文将就以上观点进行分析,并为设计师提供制作高品质全速测试程序的一些建议。

建议的方法

使用芯片上用于测试目的的功能时脉获得比外部时脉更高精密度的结果。确保自动测试程序产生(ATPG)工具能够利用芯片上时脉和时脉逻辑实现全速测试图案。

如果组件的制造特征尺寸在130nm以下,应在测试仪器中增加转换故障模型测试图案。该模型可透过查找每个内部节点上的缓慢上升或缓慢下降变化检查出时序缺陷。

在测试关键路径或整体组件时序表征检查时使用路径延迟故障模型。一些公司也使用路径延迟故障模型进行速度分级。

使用静态时序分析定义和规定时脉与时序的关系,使设立和保持时间能被检查。路径的宽松时间也可以计算,有助于发现最关键的路径。这些路径再送到ATPG工具制作路径延迟图案。此外,时序例外路径也有规定。

使用能够在图案产生期间自动处理时序例外的ATPG工具。

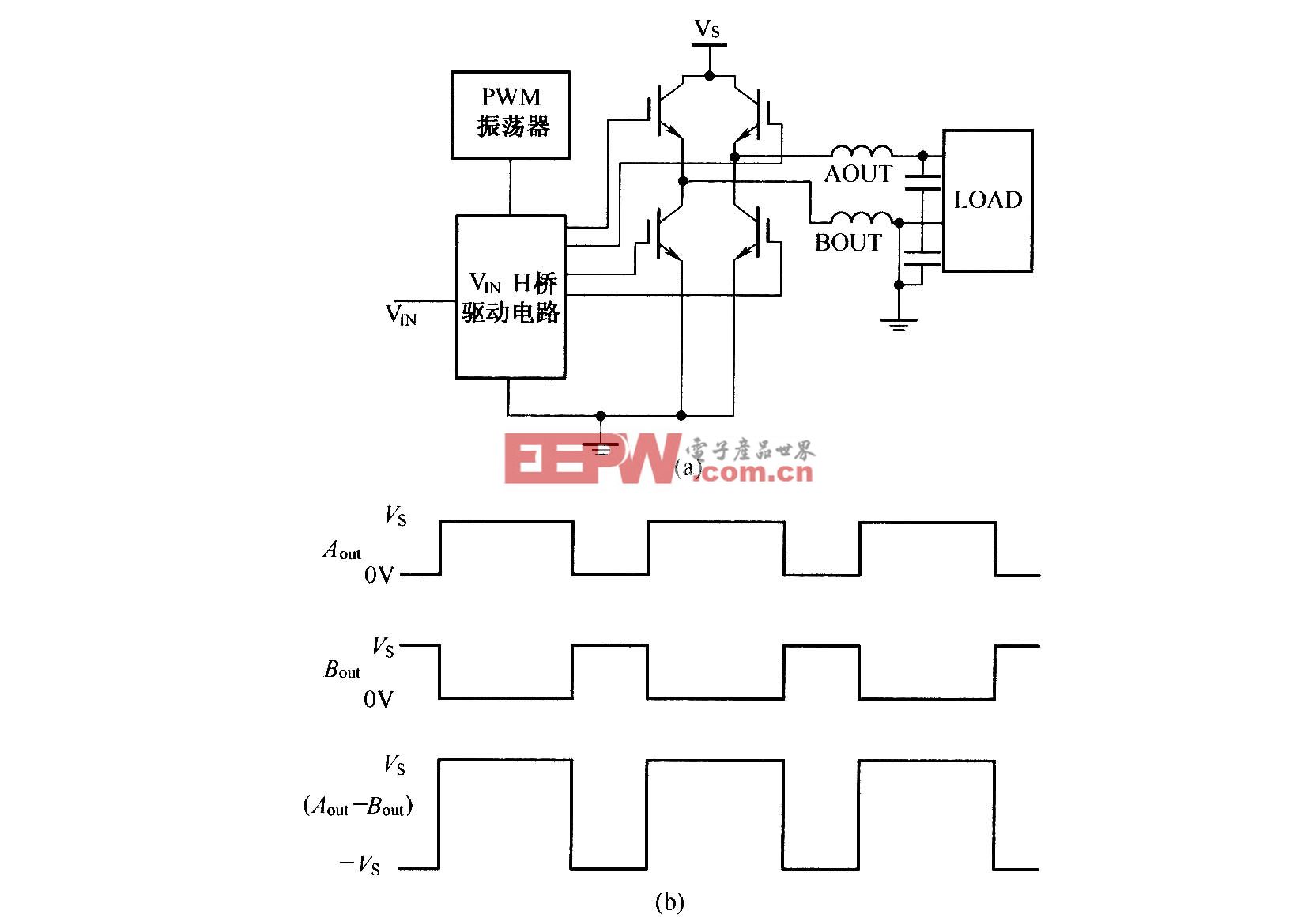

图:采用传统方法来处理时序例外路径的五个设计范例,与在SDC档案中进行读取,且仅需增加X轴的新方法比较。

不建议的方法

如果组件上已经有这些功能时脉,就不应该为了支持高速时脉而在复杂的自动测试设备上花费太多的时间。一些接脚的I/O焊盘无论如何都无法处理很快的外部时脉速度。

采用130nm以下制程制造的设计不应该依赖连续故障模型。许多相关论文指出,随着几何尺寸的缩小,缺陷与时序的关系将越来越密切。许多问题与在组件上制作小于制造用微影波长的特征尺寸和外形有关。

不解决故障和多周期路径就制作全速测试图案。如果这些问题不解决,ATPG工具制作的测试图案期望值将是组件无法实现的,极易导致测试图案的仿真失配,并可能使好的组件无法通过测试。

在ATPG过程中只约束X轴的时序例外路径端点。这种传统方法将降低测试覆盖率,并导致测试图案仪上有更多的X点。它会屏蔽掉适用于其它全速测试路径的观察点,使芯片的某些部份无法被测试到。

评论