Launch-off-shift实时测试

通过全面跳变样本(broadside-transition-pattern)和 launch-off-shift 技术的比较,表明后者可以用于测试 90 nm 无线基带器件。

在对 0.13mm以下工艺器件的制造进行实时(at-speed)测试时,Launch-off-shift(LOS)与全面跳变样本技术都有各自的用途。Broadside-transition-pattern 方法更常用,但我们将两种技术针对无线基带器件进行了测试,结果表明 LOS 更有优势。

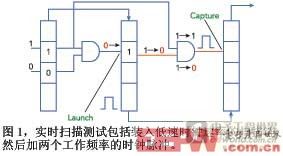

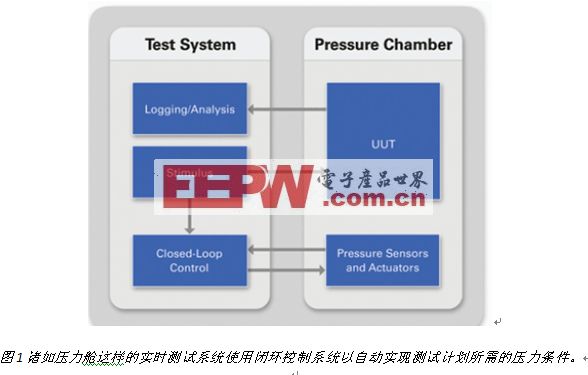

实时扫描测试用于静态测试无法胜任的应用(参考文献 1)。实时扫描测试的基本步骤是,以低时钟速率装入扫描链,然后加上两个工作频率的时钟脉冲(图 1)。第一个脉冲产生一个跳变,从一个扫描单元启动一个传播。第二个脉冲在被测路径的末端捕捉扫描单元值。

如果电路工作正常,则跳变将及时传播到路径的末端,并捕捉到正确的值。否则,如果有一个延迟造成慢速传播,则从触发到捕捉之间的跳变将减缓,并捕捉到错误值,这样就检测到了缺陷。

最常用的实时扫描图形是跳变样本(transition pattern,参考文献 2)。设计中每个

门的端子都对可能的缓升(0 至 1)和缓降(1 至 0)缺陷建立了模型。自动测试程序生成(ATPG)工具以这些故障点为目标,用所有触发扫描单元产生一个跳变,并用下游的任何扫描单元捕捉结果。

用PLL作精确时钟

实时扫描测试的一个重要问题是如何为实时的触发和捕捉脉冲施加精确的时钟。传统的保持(stuck-at)扫描样本是静态的。用于装入扫描链和捕捉结果的保持时钟频率一般在 10 MHz 和 40 MHz 之间。实时扫描测试可以使用类似保持测试中的时钟频率来装入扫描链,但必须以工作频率施加触发和捕捉脉冲。

随着所需频率的增加,用一台测试仪为触发和捕捉提供实时时钟越来越吃力。有一种方案是围绕器件内部锁相环(PLL)采用一些基本的编程能力,它提供了一种不错的选择(参考文献 3)。为实时测试提供内部 PLL 控制已成为实时扫描测试的一种常用做法(参考文献 4 和 5)。

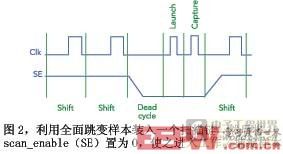

实时跳变图形应用中最常见的技术被称为全面或 launch-from-capture 样本类型(参考文献 6),见图 2。采用这种样本类型时,扫描链被装入,然后将 scan_enable(SE)强制置 0,使扫描链进入工作/捕捉模式。有些时候,不活动的测试样本要额外增加一个循环,以确保 scan_enable 的完全稳定。然后,生成两个脉冲来触发和捕捉该跳变。

全面样本在工作模式下触发跳变,因此可能会沿着实际工作路径传播跳变。通常情况下,全面样本的 ATPG 覆盖报告可以比标准的静态保持样本少 10%。

Launch-off-shift 样本

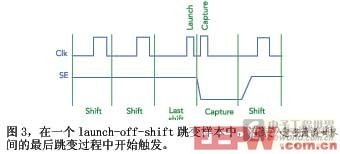

采用 LOS 样本时(图 3),触发在装入扫描链时的最后跳变期内发生。然后,电路非常快地被置为工作/捕捉模式,从而可以产生一个实时工作时钟。

与全面样本相比,用 LOS 的 ATPG 更加简单。它是在最后跳变前的一个跳变期间,对一个跳变将起始值直接装入扫描单元的一次简单的 ATPG 动作,然后在最后跳变时装入跳变值。全面图形需要 ATPG 计算出通过组合逻辑的跳变值,因为它在触发脉冲期间是处于工作模式。另外,LOS样本报告的覆盖通常高于全面样本。

LOS 可报告较高的覆盖,并使 ATPG 更加简单,因此与全面样本相比,它有较少的样本和更快的 ATPG 运行时间。那么,为什么全面跳变测试要比 LOS 样本更常用呢?

有两个主要原因限制了 LOS 样本的应用。首先,难以在最后跳变和工作时钟脉冲之间使电路从跳变模式改变到工作/捕捉模式。如果采用标准的 scan_enable 结构,则 scan_enable 必须发送一个时钟。此外,由于 scan_enable 要接到所有时序元件上,因此它是一个全局时钟,必须保持在系统时钟频率上。解决这个问题的一个方法是为 scan_enable 在整个器件中增加流水线逻辑(参考文献 7)。

流水线 scan_enable 为设计增加了额外的测试逻辑,但它避免了将 scan_enable 作为一个全局时钟的困难工作。如图 4 所示,时钟在本地 scan_enable 中触发了一个变化。

采用 LOS 样本的另一个常见问题是,也许会通过功能不正常的路径来测试电路。LOS 样本可以在一次跳变中改变,而在正常的电路工作期间不可能出现这种跳变。

还有一个重要问题,即超出全面样本的覆盖中,有多少是来源于非功能逻辑?有可能出现这种情况,在实时测试期间,测试的非功能逻辑会报告虚假故障,从而导致良率损失(参考文献 8)。

评论