基于FPGA的软件无线电高速数字信号处理

摘 要 本文首先建立了单信道的软件无线电数学模型,分析比较了FPGA、ASIC以及DSP设计方式的优缺点,并深入研究了FPGA技术在软件无线电中的应用。

本文引用地址:https://www.eepw.com.cn/article/249221.htm1 引言

软件无线电的基本思想是:A/D、D/A变换器尽可能地接近天线,用软件来完成尽可能多的无线电台的功能1软件无线电的结构大致分为三种:射频低通采样数字化结构、射频带通采样数字化结构和宽带中频采样数字化结构。

对于前两种方式,由于是对射频信号直接进行采样,结构简洁,并把模拟电路部分减小到最低限度,无疑是最理想的方式,但这种结构不仅对A/D转换器的性能如转换速率、工作带宽、动态范围提出了非常高的要求,同时对后续DSP或ASIC的处理速度要求过高,以至于无法实现;宽带中频采样的软件无线电结构与目前的中频数字化接收机(发射机)的结构是类似的,都采用了多次混频体制,在适当的中频位置进行数字化,所以它是三种结构中最容易实现的,对器件的要求也较低,但它离理想软件无线电的要求仍有一定距离。

2 单信道软件无线电数学模型

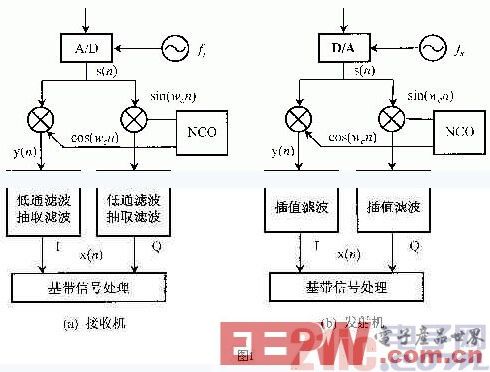

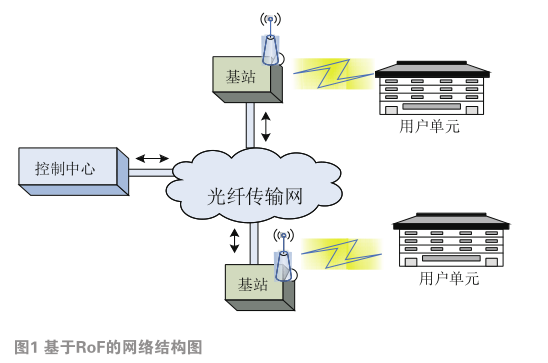

单信道软件无线电接收机和发射机的数学模型如图1所示。以接收机为例,将数字处理流程分为两部分:一是数字下变频部分,包含NCO、混频器、低通滤波以及抽取滤波器;二是基带信号处理部分,包含解调、译码、自适应均衡、帧调整、比特调整和链路去加密等算法。数字下变频单元的功能一是进行频谱搬移,将射频信号或中频信号转换为零中频信号;二是降低采样速率,将满足射频或中频采样定理的高速采样信号降低为低速基带采样信号。

就目前器件的发展水平,要想实现完全的射频数字化,几乎还不太可能,所以研究的重点往往放在中频数字化上。根据上面的分析,中频数字化中基带信号处理部分由于处在较低速率上,一般采用通用DSP方案实现,通过软件来实现各种功能;而对于数字变频部分,它们过高的速率使得通用DSP无能为力,即使像运算速度已高达600 MHz的TMS320C64X也不能解决数字中频的处理,所以,如何解决A/D采样后高速信号的处理,依然是中频以下软件无线电的关键。目前,人们已经提出了一些解决关键元器件的方法,并已出现了大量的数字中频产品,尤以Harris公司和Gray公司为代表,像Harris公司的可编程数字上/下变频器 HSP50415、HSP50216等都为软件无线电的实现奠定了良好的基础。同时,在另一方面,由于FPGA技术的迅速发展,超大规模、高速度的 FPGA芯片不断出现,特别是像Xilinx公司的SpartanII、VirtexII具有独特的快速逻辑进位、DDL功能,为实现高速数字信号处理提供了可能,这种FPGA加DSP的设计方法为实现软件无线电提供了一种更加灵活的方案,本文的重点正是研究FPGA技术在软件无线电中的应用。

3 几种技术方案的比较

3.1 FPGA的发展现状

FPGA(Field Programmable Gate Array)现场可编程门阵列是最近10年发展起来的新型可编程逻辑器件。由于FPGA器件的功能由逻辑结构的配置数据决定,工作前需要从芯片外部加载配置数据。配置数据存储在片外的EPROM或其它存储体上,人们可以控制加载过程,在现场修改器件的逻辑功能,即所谓现场编程。FPGA与CPLD一起在数字电路中发挥着巨大的作用。FPGA技术的发展可以从全球最大的FPGA生产厂商Xillinx公司推出的产品看出,无论是在规模、处理速度还是功耗上,都得到了长足的进步,如VirtexII系列XC2V10000:系统逻辑门为10M,内含专用18(18位乘法器192个,并有Block RAM 3456kbit,内部时钟处理速度为420MHz,IO数据速率可达840Mbit/s,核心电压1.5V。

3.2 FPGA与ASIC的比较

下面我们从功耗、体积、成本、现场可编程性以及硅芯片的解决方案等角度分别对高速DSP、ASIC以及FPGA设计方案进行比较,如表1所示。

从表1中可以看出,与ASIC设计方案比较,FPGA具有更大的灵活性。ASIC设计是通过在FPGA中的模型来测量,当接近要求时,再转到小批量ASIC 中测量,这种测量是需要反复进行的。设计系统直接使用可重构的FPGA,不但增加了设计的灵活性,而且大大减少了投放市场所需的时间。

3.3 FPGA与DSP的比较

DSP芯片在市场上已有20几年了,其性能也在不断地提高,但要达到千兆赫量级的时钟速度所要求的功耗仍然较高,并且其串行处理的结构不可能实现高阶的数字滤波器功能(如表2所示)。

4 FPGA在数字中频处理中的应用

根据图1所示数学模型,FPGA在软件无线电中的应用主要体现在数字上变频DUC和数字下变频DDC中。经过 A/D采样后的信息直接送给FPGA,在FPGA中完成本地混频,把中频信号搬移到基带信号,然后经过低通滤波和多级抽取滤波,降低信息的采样速率,由 FPGA送至通用DSP,实现基带信号的调制解调;对于数字上变频结构,和下变频有完全对称的结构,所以分析时仅以接收机为例。

4.1 本地频率产生器和混频器

DDC结构中第一个环节就是要实现本地数字混频,主要由两个部件完成,一是乘法器,二是数控振荡器(NCO)。乘法器是数字信号处理中的基本运算单元,在FPGA中设计较为复杂,而且占用资源也比较多,但在具体实现FIR滤波时,往往不采用这种直接的乘累加的形式,以免占用大量的资源;在实现混频时,由于只需两个乘法器,而且是在很高的速率下进行,所以不考虑资源的限制。在Xilinx公司FPGA产品中,有的已在芯片内部嵌入了乘法器,这种内置乘法器充分结合了芯片硬件特点,使得运算速度更高。

NCO的硬件结构如图2所示,主要由相位累加器和SIN/COS表构成。相位累加器产生的相位作为地址去查找ROM表,查到的SIN/COS值即本地载波的数字频率送至乘法器,完成混频。在实现NCO时有以下参数值得注意:

· NCO产生数字频率的精度。此参数与SIN/COS 值的位数有关,位数越宽,则精度也就越高,但占用FPGA的资源也就越多。

· 载波的同步。如果需要本地载波做到严格的同步,则需要额外的锁相环结构获取偏移相位,进行调整。

· NCO输出频率的噪声。噪声的产生与频率在时间上量化有关,由于采样时刻不一定严格对齐载波的相位,所以会产生噪声,但构造更大的正弦或余弦表会减少噪声分量,这同样会增加FPGA的资源占用。

4.2 抽样率变换滤波器组

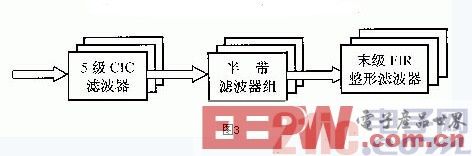

下变频过程中经过混频后的信号必须进行抽取滤波,以便降低抽样速率,使得通用的DSP对基带信号处理时有充足的时间完成运算;同样,在上变频过程中,首先要进行插值滤波,提高抽样速率,从而实现在IF范围内频谱的搬移。根据DDC总抽取因子的大小,我们把数字下变频分为两类:即当抽取率大于32时,认为是窄带下变频,反之则认为是宽带下变频。无论是宽带还是窄带,一般都采用FIR结构实现抽取滤波器,但对于窄带下变频,由于抽取因子较大,所以其抽取滤波器组也更为复杂一些。参考古得曼(Goodman)和开莱(Carey)提出的设计多级抽取器和内插器的经典模型[3],对窄带下变频作如图3设计,其中CIC滤波器为整系数滤波器,滤波时无需乘法运算,而半带滤波器有一半系数为零,这样在滤波时大大减少了计算量。

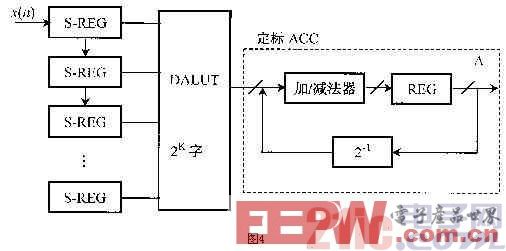

实现FIR滤波功能的基本元素包括乘法器、加法器、延迟单元以及存储单元等,其中乘法器的设计最为复杂。用 FPGA技术作乘累加运算通常有移位相加、加法器树、查询表和逻辑树等设计方法,不管采取哪种方法,要实现一个高阶的数字滤波器都将占用相当大的资源。相比较来说,采用分布式运算DA算法(Distributed Arithmetic)的FPGA设计无论是在逻辑资源占用上,还是处理速度上都具有很大的优势,特别是对于基于SRAM结构的FPGA更加适合于DSP 功能的设计。有关DA算法早期比较著名的阐述,是在1974年由Abraham Peled 和Bede Liu在讨论数字IIR滤波器和FIR滤波器硬件设计时涉及到,1975年在IEEE Proceedings中Freeny发表了一篇关于DA算法在贝尔实验室电话系统中应用的论文,同时惠普公司的Kai-Ping Yiu提供了一种有关符号位的DA设计方法;此后,西门子H.Schroder以及RICE大学C. S. Burrus 在提高算法的处理速度方面做了深入的研究。随着大规模集成电路技术的发展,特别是可编程逻辑器件的发展,DA算法在数字滤波器硬件设计中的研究进一步加强,SDA(串行DA)算法和PDA(并行DA)算法已成为FPGA实现DSP功能最为有效的方法。根据DA算法设计的思想,我们进行FIR滤波器设计如图4所示。

图4为FIR滤波器实现的串行DA形式,其中S-REG为串行移位寄存器,实现输入数据的并/串转换,并由 TSB(Time-Skew Buffer)完成数据的移位缓存,产生访问DALUT的地址;查表后得到的输 出数据由定标ACC单元完成累加,累加的结果即为滤波后的值。SDA算法处理的速度与抽头系数的大小无关,只与输入信号的数据位数有关,例如当x(n) 的数据宽度为12bit,则需要12个时钟来完成一个输出结果的运算。PDA(并行DA)算法可相应提高信号处理的速度,但它是以牺牲更大的逻辑单元为代价的。为了实现较高性能的滤波器指标,往往需要很多个抽头,这时DALUT必然会占用很大的空间,如每增加一个抽头,DALUT的容量就会增加一倍 (2K),在实际处理时,通常采用分解级联的方法,利用多个DALUT实现总的滤波功能。

4.3 FPGA实现和实验结果

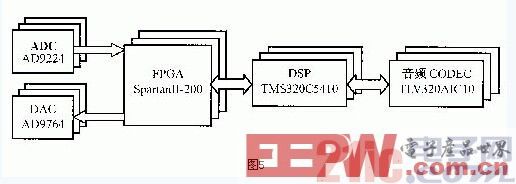

我们设计了一个中频为10.75MHz,带宽为20kHz的中频数字化收发信机,硬件设计如图5所示。

如图5所示,中频A/D、D/A分别采用AD公司的AD9224和AD9764,其中AD9224分辨率为 12bit,AD9764为14 bit,采样速率为30.720MHz;DSP选用TI公司的0芯片,最高处理速度为100MIPS;音频A/D、D/A由 TLV320AIC10实现。FPGA选用Xilinx公司的SpartanII-200,规模为20万门,最高工作频率为200MHz,该芯片主要完成抽取率为512的DDC功能和插值率同样为512的DUC功能,而且是在同一片FPGA中实现。FPGA单元与DSP接口的数据速率为60kHz。 FPGA开发工具为Xilinx Foundation3.1,编程语言采用VHDL和Schematic混合设计方法,并利用CORE Generator提供的DA FIR滤波器方便地实现半带滤波器和整形高阶FIR滤波器功能。

5 结束语

本文在建立单信道软件无线电数学模型的基础上,深入研究了FPGA技术在软件无线电高速数字信号处理中的应用,特别是在DDC和DUC中的应用。研究表明,这种基于FPGA/通用DSP的协同设计方法,无论是在性能价格上,还是在设计的灵活性上,都有很大的优势,非常适合目前软件无线电硬件平台设计。

参考文献

1 Mitola J. The software radio architecture. IEEE Communication Magazine,1995(5)

2 Cummings M, Haruyama. FPGA in the software radio. IEEE Communications Magazine, 1999,37(2)

3 R.E.克劳切,L.R拉宾纳.多抽样率数字信号处理.北京:人民邮电出版社,1988

滤波器相关文章:滤波器原理

dc相关文章:dc是什么

fpga相关文章:fpga是什么

西门子plc相关文章:西门子plc视频教程

滤波器相关文章:滤波器原理

混频器相关文章:混频器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理

评论