IC时钟分配系统中的PLL

闪烁噪声:

本文引用地址:https://www.eepw.com.cn/article/246164.htm闪烁噪声用1/f表示,该噪声在偏移角频率fc处拦截热噪声底限,其频谱与1/f相关。所有有源设备以及碳质电阻器等部分无源组件中均可发现该噪声。闪烁噪声的特点是,其大小与所观察到的信号频率成反比。闪烁噪声是通过其频率依赖性得到识别的,但其成因尚未明确。频率小于100Hz时,闪烁噪声将变得突出。使用绕线或金属薄膜电阻器替代更加常见的碳质电阻器,便可大幅降低闪烁噪声。

白噪声:

噪声的功率谱表明了任何给定频率下噪声功率的集中度。许多噪声源均为“白色”,即其功率谱具有平坦性,即便在极高频率时也是如此。换而言之,白色噪声为常量值,与频率无关。恒定带宽的信号功率不会随频率变化而变化。绘制其与频率关系图便可发现,白色噪声为图5中水平线所示的恒定值。

PLL内的相位噪声

PLL属于振荡器类别之一,而在任何振荡器设计中,频率稳定性至关重要。高性能时钟分配系统中,由于相位噪声直接影响系统整体性能,故成为关键的考虑因素。其噪声既可由各独立模块固有噪声源产生,也可因电源噪声及衬底噪声等外部噪声源与各模块耦合后而产生。事实上,PLL内所有模块均会或多或少地产生输出相位噪声。

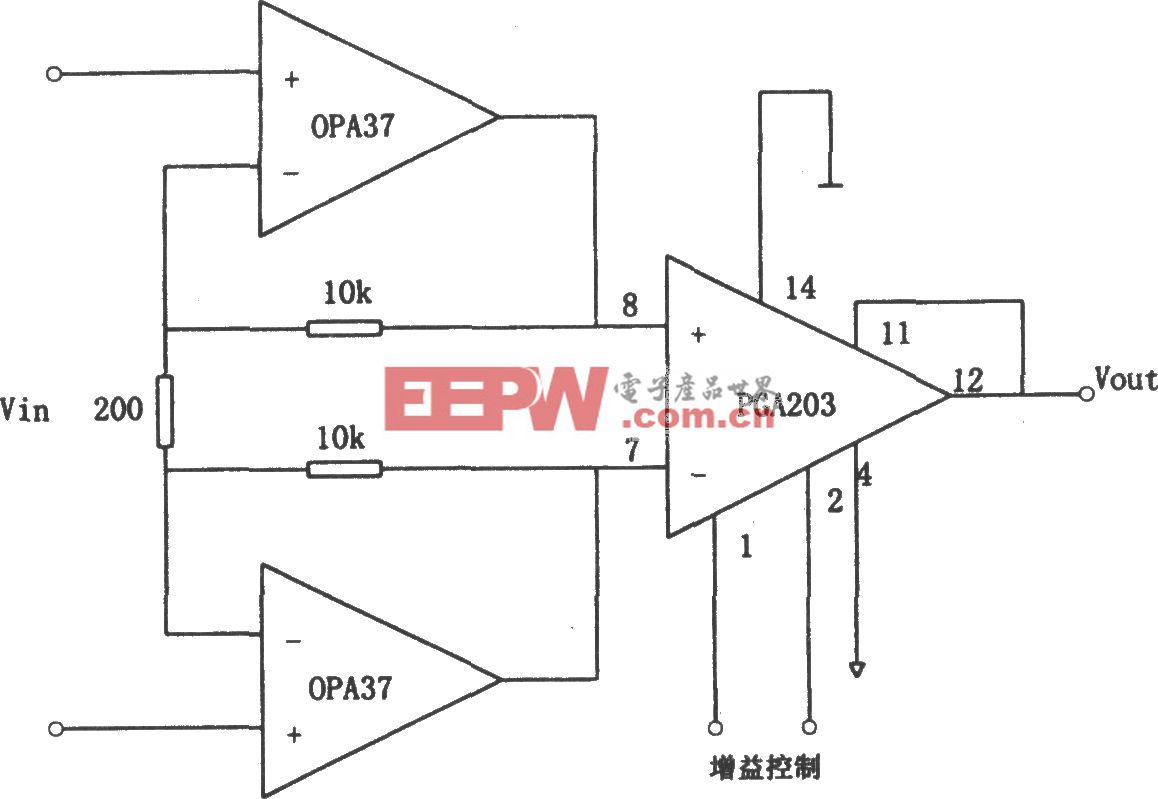

研究总体相位噪声的模块前,让我们再次回顾一下PLL的方框图,如图7所示。

基准和VCO噪声:

PLL有两大噪声源,即对PLL整体相位噪声产生影响的基准振荡器和VCO(电压控制振荡器)。基准噪声源包括时序源噪声、PCB噪声耦合噪声及电源噪声,VCO噪声源则包括环路滤波器组件、VCO放大器噪声和电源噪声。

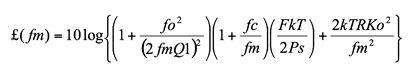

理想的VCO不会产生相位噪声,且从频域角度观察时呈单一谱线,但现实情况并非如此,因为VCO的输出抖动会产生扩频,进而生成相位噪声。可通过利森(Leeson)方程式充分理解VCO噪声,同时还可通过对该方程式的研究,找到降低VCO噪声的方法。表示振荡器相位噪声频谱的利森方程式如下:

式中:

£(fm) 为偏移时的功率比

fm为振荡器所生成的总输出功率中的1Hz频带(单位:dBc/Hz)

fo为载波频率

fm为偏移频率

fc闪烁转角频率

Q1为谐振器的负载Q值(负载Q值指包括外部组件影响在内的品质因数)

F为噪声因数

kT为室温条件下的波尔兹曼常数

Ps为振荡器输入端的平均功率

R为调谐二极管的等效噪声电阻

Ko为振荡器的电压增益。

光耦相关文章:光耦原理

电容器相关文章:电容器原理

万用表相关文章:万用表怎么用

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 锁相环相关文章:锁相环原理

评论