TMS320C6727的音频采集处理回放系统设计

引 言

数字信号自从出现以后就以其无与伦比的优势迅速打破了原来模拟信号一统天下的局面。随着音频处理技术的发展,音频处理算法越来越复杂,采用传统的模拟信号处理的办法来实现这些算法不仅难度大,成本高,有的甚至根本无法实现。然而,由于数字信号处理器(DSPs)速度的不断提高,这些复杂的音频处理算法可以很容易地通过DSPs实现,因此如今很多音频处理采用DSPs实现。然而原始的音频信号都是模拟的,如果采用数字信号处理技术进行音频处理,首先要面对的就是音频采集、处理和输出系统问题。

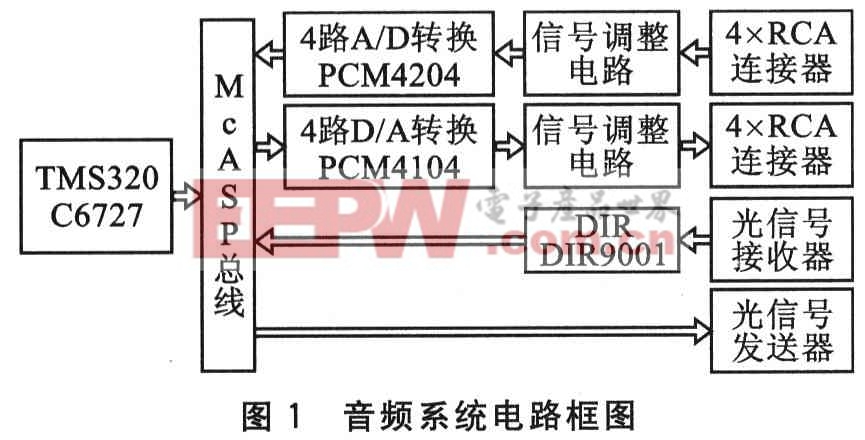

本文介绍了一个8路模拟音频输入、8路模拟音频输出、1路数字信号输入和1路数字信号输出的音频处理系统。分析系统的硬件连接和功能实现方法,以及系统的软件工作原理。

1 设计方案

系统设计框架如图1所示。数字信号处理器选用TI公司的32位浮点DSPs TMS320C6727,A/D转换部分采用2片TI公司的音频模/数转换芯片PCM4204,D/A转换部分采用2片TI公司的音频数/模转换芯片PCM4104,数字信号接收部分选用数字音频接收接口芯片DIR9001。

TMS320C6727是TI公司推出的一款专门用于音频信号处理的高速、浮点DSPs。其高达300 MHz的频率再加上32位的浮点处理能力,使得它可以轻松运行各种复杂的音频处理算法,满足系统实时性的要求。另外其本身带有3个McASP接口,支持I2S、TDM、S/PDIF等多种音频传输格式,可以实现与其他音频设备的无缝连接。

PCM4204与PCM4104分别是4通道、24位、216kHz采样频率的模/数和数/模芯片。其中PCM4.204支持左校验、右校验、I2S等数据传输格式,且主/从模式可以设置;PCM4104支持左校验、右校验、I2S等数据传输格式,软静音(soft mute)模式,软/硬两种控制方式可供选择。

DIR9001用于接收采样频率在24~108 kHz之间的双相编码信号,输出格式为I2S、左校验、右校验等。

2 硬件电路

音频系统硬件电路分为音频采集、音频回放和通信3个部分。音频采集部分实现模拟音频信号转换成数字音频信号并传入TMS320C6727;音频回放部分实现数字音频信号从TMS320C6727输出并转换成模拟音频信号驱动扬声器;通信部分实现与其他音频设备间的数据传输。音频数据的采集传输与通信都通过TMS320C6727的McASP口完成。TMS320C6727有3个McASP口:McASP0、McASPl、McASP2口。其中McASP0口有16个串行数据口AXR0~AXRl5,McASPl有6个串行数据口(共用AXR8~AXRl3),McASP2有2个串行数据口(共用AXRl4、AXRl5)。音频采集与回放使用McASPO的AXR0~AXR7,音频数据通信发送采用McASP0的AXRl4,接收采用McASP2口。

PCM4204与PCM4104的时钟由PLL1707组成的时钟电路产生,时钟频率为24.576 MHz(256fs,fs为采样频率)。每个McASP口的接收数据时钟和发送数据时钟是相互独立的,并且都有自己的主时钟(AHCLK),当McASP接口为I2S提供时钟信号时,BCK和LRCK除可以从系统时钟得到外还可以从AHCLK分频得到。

2.1 音频采集电路

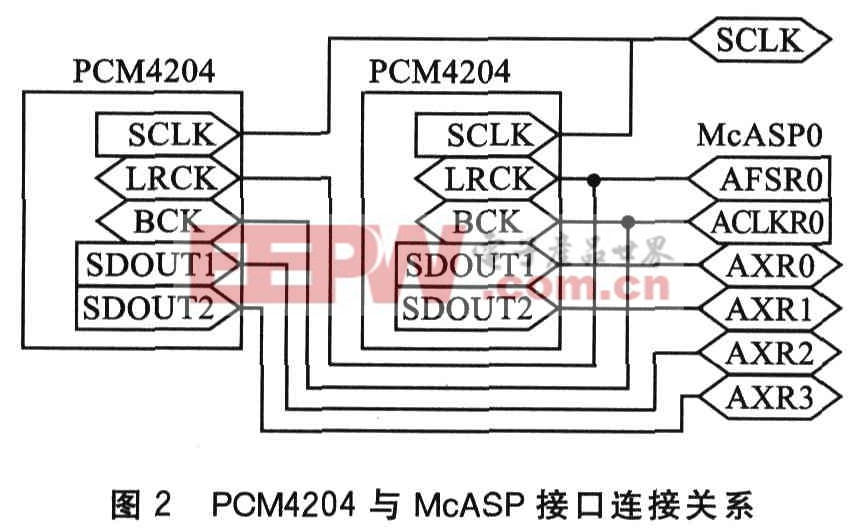

音频采集电路连线图由图2给出。因为本文重点不在前端调理电路,所以图中只给出了PCM4204与TMS320C6727的MeASP0口之间的硬件连接关系。

PCM4204与McASPO口之间的数据传输格式选用I2S总线。I2S总线有3种主要信号:位时钟(BCK)、帧时钟(LRCK)和串行数据。

PCM4204有Master/Slave(主/从)两种工作模式:当工作在Master模式时,PCM4204产生BCK信号和LRCK信号;当工作在Slave模式时,PCM4204接收BCK信号和LRCK信号。TMS320C6727的McASP接口同样可以接收BCK信号和LRCK信号。考虑到McASP接口的BCK信号和LRCK信号由DSPs的内部时钟分频得到,无法得到音频所需的精确时钟信号,因此BCK信号和LRCK信号由PCM4204产生。为了防止2片PCM4204同时设为Master模式而造成时钟信号混乱,把其中一片设置为Master模式,另一片设置为Slave模式。工作在Master模式的PCM4204同时为McASP0口的接收时钟和另一片PCM4204提供BCK信号和LRCK信号。

McASP0口的AXR0~AXR3设置为接收模式分别与2片PCM4204的信号输出端相连,用于接收从PCM4204发出来的串行数字音频信号。

2.2 音频回放电路

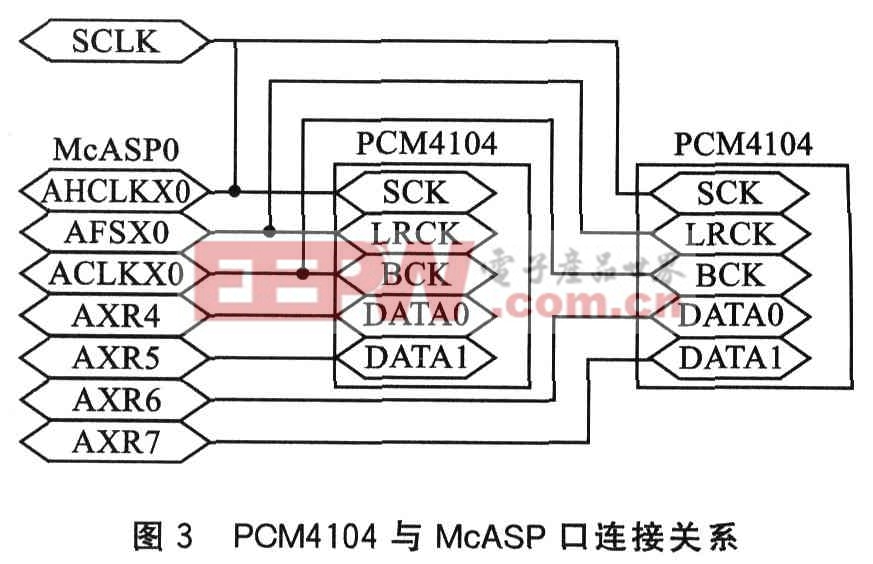

音频回放电路完成数字信号到模拟信号的转化和播放。音频回放部分连线图如图3所示。

PCM4104只能工作在Slave模式,所以要由McASP口的AFSX0和ACLKX0提供时钟信号。为了保证音频回放的采样频率与音频采集的采样频率相同,AFSX0和ACLKX0提供的时钟信号从AHCLKX0分频获得,AH—CLKXO由时钟电路提供24.576 MHz的时钟信号。同样,PCM4104的系统时钟也由时钟电路提供。

McASP0口的AXR4~AXR7设置为发送模式并与PCM4104的信号输入脚相连,实现串行数字音频信号的回放。

2.3 音频通信电路

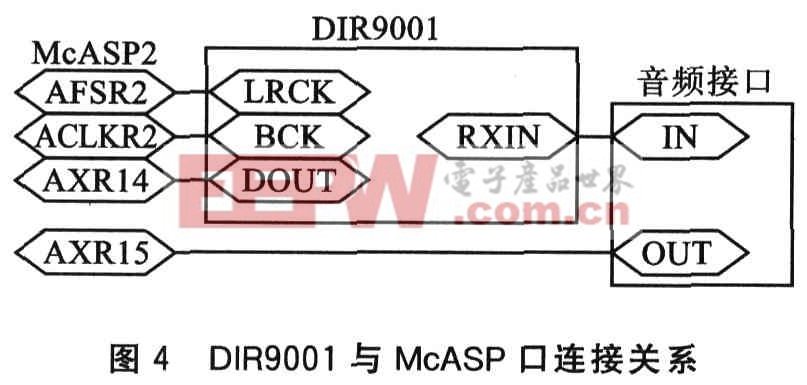

音频通信电路能够实现音频系统与其他设备之间的数据传输。传输格式为S/PDIF,采用双相标识编码(Biphase—Mark Code,BMC)。McASP接口支持该传输方式,可以直接从McASP口输出。对于信号接收,通过数字音频解调芯片DIR900l把BMC信号转化成I2S格式并传输给McASP2口的接收端。硬件连接如图4所示,McASP2作为接收端,接收经DIR9001解调后的数字音频信号。MeASP2的AXRl5端口设为输出端口,以BMC格式输出音频数据。

3 音频系统硬件配置

3.1 PCM4204设置

PCM4204的控制引脚用于设置其工作方式。其中引脚S/M用于选择主/从模式,FSO、FSl、FS2用于选择采样模式(sampling mode),FMTO、FMTl、FMT2用于选择音频数据格式(audio data format)。2片PCM4204的引脚配置如下:

PCM4204有3种工作模式:Single Rate、Dual Rate和Quad Rate。根据以上配置信息,PCM4204采样模式设置为Dual Rate模式;采样频率fs为系统时钟的1/256,即96 kHz;数据输出格式为I2S。

3.2 PCM4104的配置

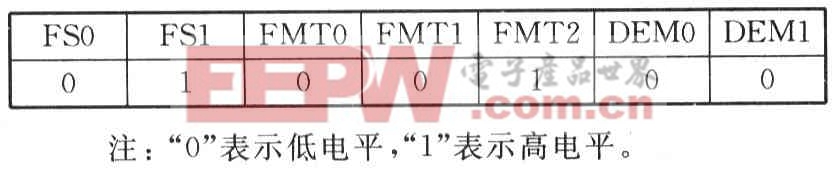

PCM4104分为软件配置和硬件配置,本设计采用硬件配置。其中引脚FSO、FSl用于配置采样模式;FMTO、FMTl、FMT2用于选择接收数字音频信号的格式;DEM0、DEMl用于选择去加重。其配置如下:

PCM4104也有3种工作模式:Single Rate、Dual Rate和Quad Rate。根据上述配置情况,PCM4104配置为DualRate数据接收模式;数据接收格式为I2S;无去加重。

4 系统软件设计

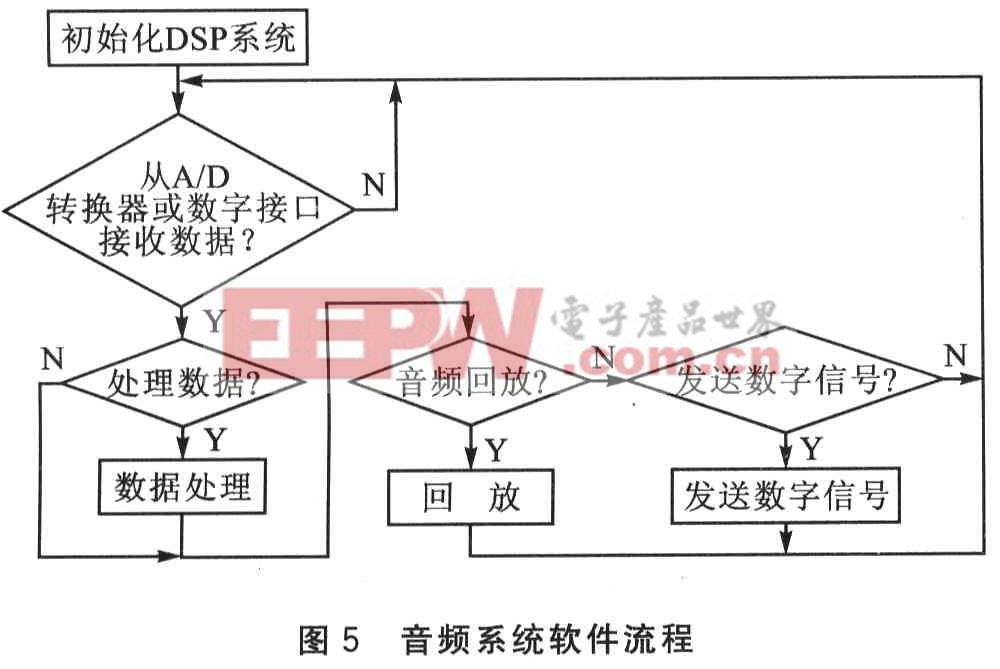

系统软件在TI公司的DSP集成开发环境CCS3.3下用C语言编写,其软件流程如图5所示。

初始化程序包括DSPs TMS320C6727的时钟、中断、McASP口的配置,以及PCM4204和PCM4104的配置等。初始化结束后PCM4204开始采样,数据传输到McASP0口的接收缓冲寄存器RBUF[O]~RBUF[3]中。如果有数字信号传入,同样被传输到McASP0口的接收缓冲寄存器RBUF[14]中。

数据处理程序可对采样后的音频数据或来自其他设备的数字音频数据进行滤波、降噪、音频编码和数据压缩等处理。

音频回放程序能够实现DSP内的数据到D/A芯片的数据传输,数字信号发送程序用于将DSPs内的数据转换成BMC格式的信号,并传给同轴电缆接头。

结 论

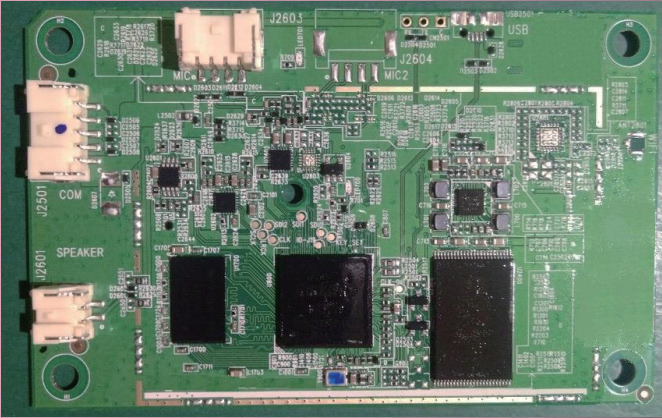

笔者设计的8路音频采集、处理、回放系统,可以实现高信噪比的音频采集和回放。在实际测试过程中,把采入的音频信号不经处理直接回放,声音效果非常好,感觉不到声音失真和延迟,并成功实现了数字音频信号loopback模式下的通信。

评论