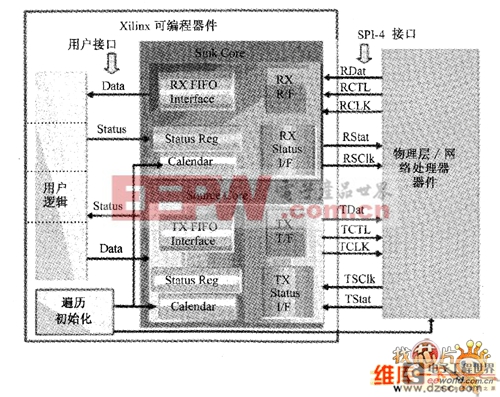

SPI-4接口的数据处理

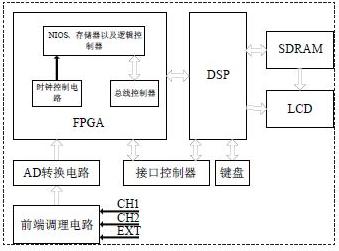

图1 Xilinx SPL-4解决方案框图

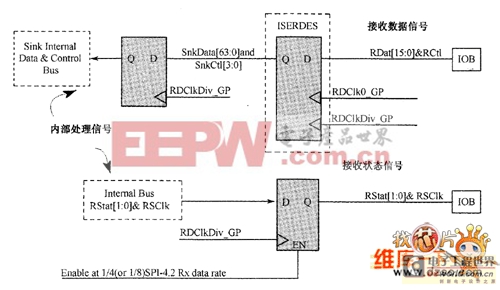

(1)Sink Core I/0接口设计

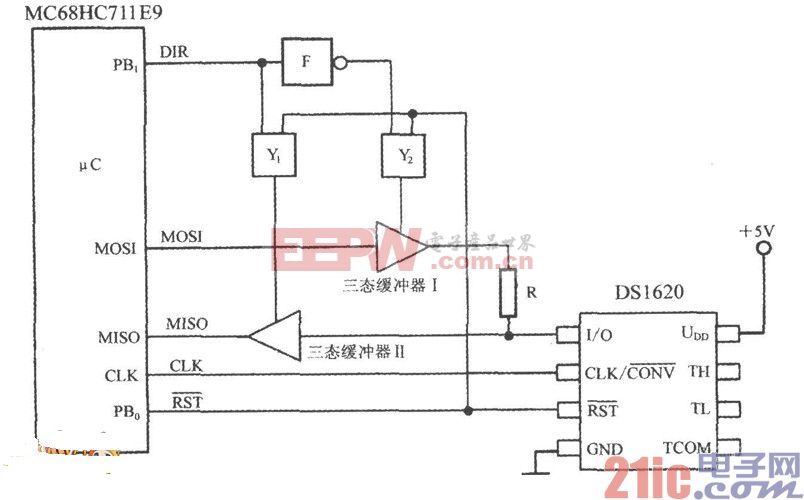

对于数据通道,Sink Core的接收数据在FPGA I/O内部通过ISERDES串并转换后,把数据速率降低供内部处理。这样做的目的是降低了FPGA内部系统频率,使时序更加容易满足。而对于状态信`患通道,把内部处理的数据直接经过LO里的寄存器锁存输出,如图2所示。

图2 Sink Core I/O接口

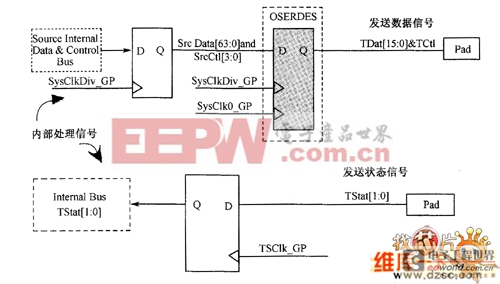

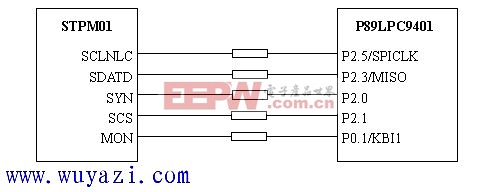

(2)Source Core I/O接口设计

Source Core的处理是内部已经处理好的数据经过FPGA I/O内部的OSERDES进行并串转换输出。而对于状态信息通道,因为速率比较低,最高不超过数据通道速率的1/4。所以处理起来比较简单,直接使用FPGA I/O内部的寄存器锁存输出到内部处理即可,如图3所示。

图3 Source Core I/O接口

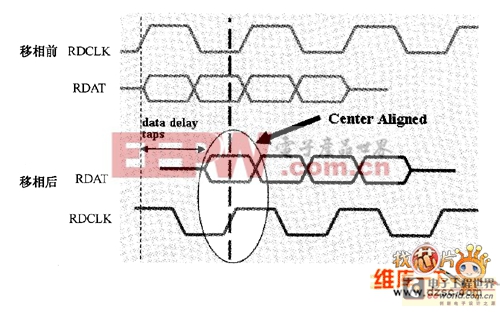

(3)DPA功能

对于数据对齐来说,由于在SPI-4中允许数据的偏移为±1个BIT,所以除了要做位对齐外,还需要做通道对齐。位对齐就是利用Xilinx Vitex-5器件内部的IODELAY模块用移相状态机在其上面进行移相。多达64级,每级大约75ps,直到采样时钟对齐到数据窗口的中间位置。位对齐的效果如图4所示。

图4 位对齐效果

通道对齐利用协议指定的Training Pattern作为对齐信息和ISERDES模块中的BITSLIP功能来进行,效果如图5所示。

图5 通道对齐前后效果

只有完成这两个对齐过程,接收端的输入数据才真正被处理完毕,这时数据就可以直接供给内部做协议处理。

(4)用户FIFO

该FIFO用于与用户逻辑连接的,其原理是把内部协议处理后的数据写入FIFO,然后读出FIFO的数据作为后级的用户逻辑使用。有机地隔离了用户逻辑和用户FIFO,使用户逻辑的设计更加清晰和容易。

(5)参数配置

该模块主要做参数配置作用,用来配置支持的端口数、最大发送包长、遍历长度及连续的DIP4和DIP2有效数目等。

评论