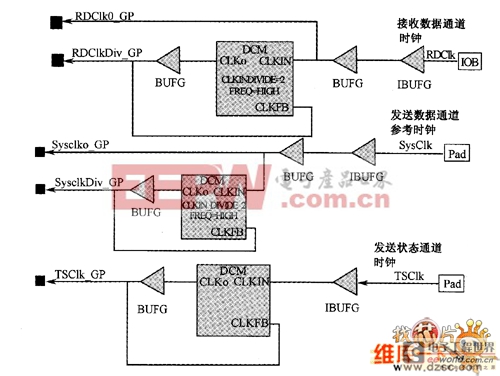

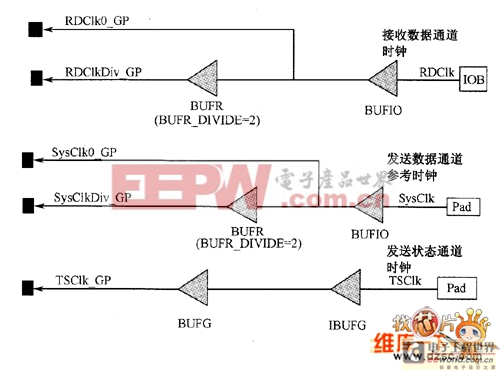

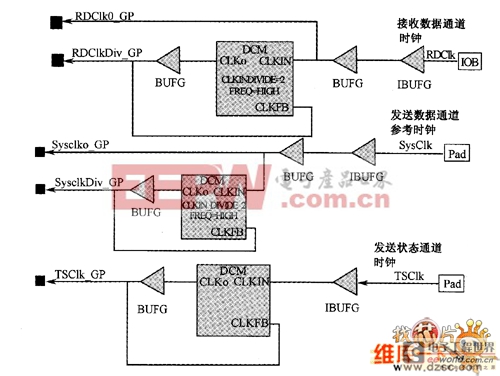

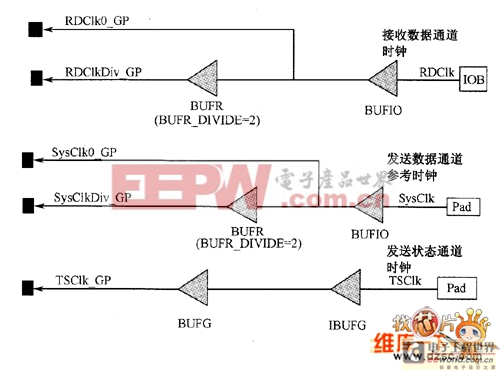

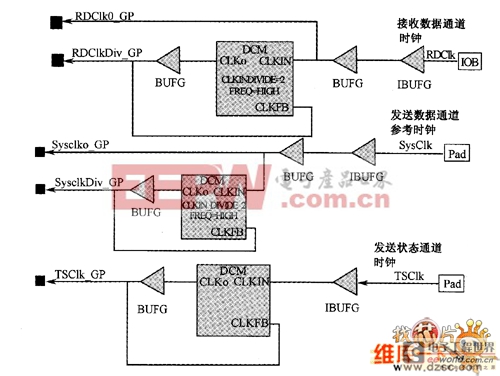

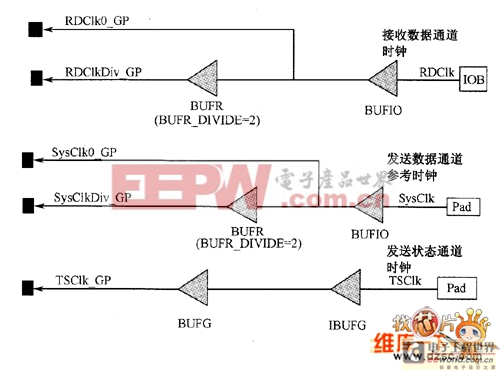

面对当今复杂的FPGA设计,时钟是至关重要的,工程的成败往往取决于它。而对于SPI-0接口设计来说,由于输入时钟高于311 MHz,并且是双沿采样的,所以时钟设计显得更加重要。对于Xilinx Virtex-5器件来说,内部提供了全局时钟和区域时钟两大时钟网络,我们分别利用这两大资源来设计SPI-4的时钟方案。全局时钟如图1所示,区域时钟如图2所示。其中,RDCLK是Sink Core的输入时钟,Sysclk为Source Core的参考时钟,TSCLK为Source Core的状态信息通道的输入时钟,用户可以根据实际情况来选择。

图1 全局时钟

图2 区域时钟

此外,TDCLK由SysClkO_GP经过FPGA的IO模块内的ODDR输出。

评论