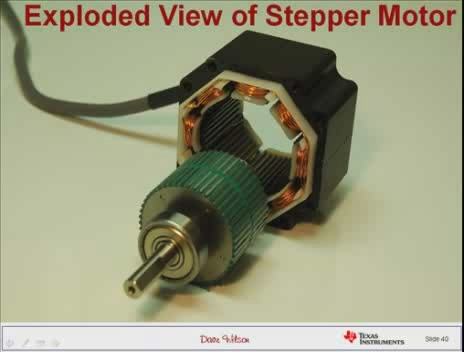

基于NiosII软核处理器的步进电机接口设计

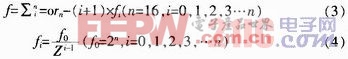

式中:f为要得到的频率;fi为各个叠加频率;f0基准脉冲;rn-(i+1)第n-(i+1)个寄存器。

文中取n=16,所以16个寄存器组成的16位二进制数的范围就是0000~FFFF。根据公式(3)、(4)可知,只要f0等于65 536 Hz,那么通过改变二进制数(r15~r0),输出f就连续可调。该电路也就是脉冲发生器(step_wave)中的核心电路。

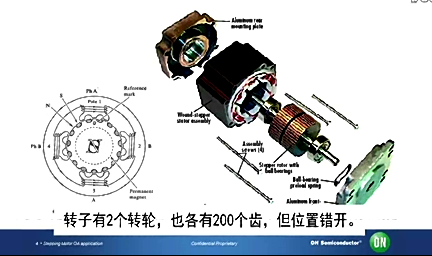

2.3 电机控制模块设计

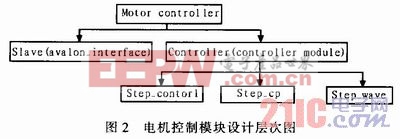

一般步进电机的控制器可以通过单片机来实现,本文电机控制模块是用verilog HDL语言实现、以IP模块的形式封装在SOPC Builder的IP模块库中,它是可以被NiosII系统直接调用的。图2为电机控制模块的设计层次图。

1)脉冲控制器

根据脉冲控制器要实现的功能,可以确定脉冲控制器主要是由以下几个小模块构成:标准频率产生模块;总输出脉冲数控制模块;输出的脉冲个数寄存器更新模块。

2)脉冲发生器

脉冲发生器的功能是产生需要的脉冲序列,经过分析后知道,此部分主要由以下几个模块构成:

①16 bit计数器,脉冲发生器最终输出的脉冲其实是由1/2CLK、1/4CLK、1/8CLK…1/32 768CLK这16种脉冲组合实现,CLK是由step _control分频得到基准时钟。为了实现这16种频率的脉冲,需要16bit的计数器。16bit计数器的产生16种状态,保持16种基频的状态唯一。

②基频产生模块,由公式(3)、(4)可知,这16种脉冲其实是以16bit计数器的16种不会重叠的状态为条件而产生的。

③脉冲叠加,脉冲叠加模块,用来把这16种脉冲叠加起来,得到需要合成的输出。最终合成的输出控制可由16个两输入与门来实现,一端接输出脉冲,另一端接对应的脉冲个数寄存器。

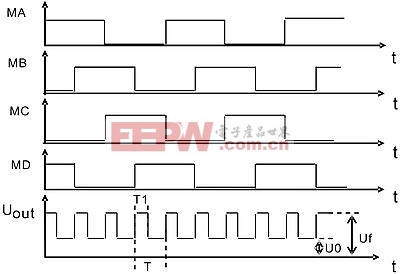

3)脉冲分相器

由于是四相步进电机,并以单拍的方式运行,所以在最后从脉冲分相器输出的频率为四相。CP[3:0]就是最终输出的四相信号。

3 电机控制模块的仿真与验证

1)功能仿真

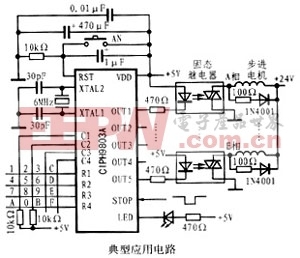

电机控制模块在Quartus II上的综合结果如图3所示,电机控制模块是由slave、step_control、step_wave及step_cp 4部分组成。

2)SOPC平台验证

首先导入的HDL文件是用于描述模块的硬件逻辑功能。对于电机控制模块,导入的文件分别是motor.v、step_control.v、step_wav e.v和step_cp.V,其中motor.V是顶层文件,配置SOPC平台,如图4所示。

评论