基于PCI总线的嵌入式实时图像处理系统

1 图像处理系统发展现状

在计算机信息处理及应用中,图像信息处理以及处理结果的应用占有十分重要的地位。图像处理的发展依赖于处理器芯片(包括单片机、DSP等)技术的应用和发展,以及大容量、价格低廉的存储器的出现。图像处理系统虽然由机箱式大体积结构发展为插卡式小型化结构,但是由于图像处理存在大量的数据信息,在实时性和容量上一般不能满足多数需要实时处理的场合。这主要体现在如下2个方面。

1.1 实时性要求

图像处理系统有很多种实现方法,比如在通用计算机上用软件实现、用单片机实现、利用特殊用途的DSP芯片来实现等。但这些实现方法都有着缺点,例如软件实现速度太慢,不能用于实时系统;单片机采用的是冯·诺依曼总线结构,而且乘法运算速度太慢;如果用特殊用途的DSP芯片又缺乏灵活性,而且开发工具不是很完善。

在本系统中,图像处理系统是在通用计算机上加入DSP加速卡来实现。利用DSP芯片的高速处理特性完成大部分的图像处理工作,计算机只是作为辅助操作和存储系统。这种方法发挥了DSP的高速性能又具有相当大的灵活性的特点,开发工具比较完善。

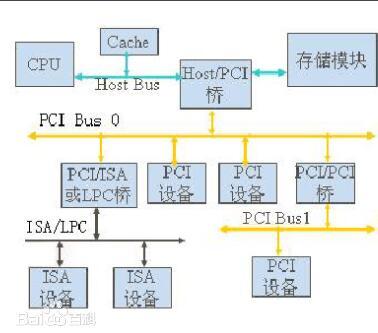

实现实时性要求还必须有足够的传输速度,PCI总线速度最高可达132MB/s,这是其他总线无法比拟的速度,如ISA总线速度只有5MB/s。

1.2 小型化要求

现今图像处理应用越来越趋于小型化系统,趋向于把整个处理系统集成在一个小"黑盒子"里面,甚至于一块电路板上。这就要求图像处理系统具有高速度、高集成度的处理芯片来完成原本需要许多部件合作完成的任务。DSP的中央处理器特性使得可以把众多的功能集于一身,并通过外部扩展来实现复杂的功能,实现系统的小型化。

另外,视频数据一个很大的特点就是大容量性,这是与音频数据最大的区别之一。对于大容量数据的实时处理不但需要高速的CPU,还需要能扩展的大容量存储空间。在通用计算机上用软件实现时,其存储空间由计算机的存储空间决定,其扩展性能受到了限制;同时单片机的扩展空间有限。它们都无法满足视频数据的大容量要求。

本文正是着眼于实时性和小型化要求这两方面问题,设计了用DSP加速卡实现的图像采集系统。利用DSP芯片的高速处理特性完成大部分的图像处理工作,上位机只完成辅助操作和存储系统。这种方法发挥了DSP的高速性能又具有相当大的灵活性,而且开发工具比较完善。另外,PCI总线速度最高可达528MB/s(66MHz、64位),这是其他总线无法比拟的速度。系统中C6000系列中DSP的可扩展存储空间高达1GB,这完全可以满足一般图像处理系统的需要。

2 DSP图像处理系统结构

本系统采用TI公司C6000系列DSP中的TMS320C6211作为系统的CPU。图像数据通过视频头输入模拟图像信号,这些信号经过视频解码芯片进行A/D转换为数字信号,经FIFO输入DSP进行图像的增强、分割、特征提取和数据压缩等,然后输出信号经PCI解码芯片转换为符合PCI总线规范的标准信号,通过PCI总线接口传到上位机。

本系统设计目的是用于智能楼宇的管理,主要实现对楼宇一些重要参数的实时检测功能等。当然可以用于其他的监控系统,其硬件系统基本一致,不同的在于软件功能的区别。系统结构图如图1。

2.1 DSP图像处理模块

本系统选用TI公司的C6000系列DSP之中的TMS320C611作为本系统的CPU。C6000是TI公司发布的面向视频处理领域的新款高速数字处理芯片,适用于移动通信基站、图像监控、雷达系统等需要高速度和高度智能化的应用领域。存储空间选用现代公司的2片HY57V651620B作为运行过程中的存储器(SDRAM)和AMD公司的AM29LV800B 作为启动时候需加载程序和参数的存储器(FLASH)。其结构如图2所示。图中的HPI(Host Port Interface)为主机口;EMIF(External Memory Interface)为外部存储器接口,兼容同步/异步方式。

TMS320C6211处理器由3个主要部分组成:CPU内核、外设和存储器。它的高速性能主要体现在如下几个方面:① TMS320C6211的存储空间最大扩展可以达到512MB,这完全可以满足各种图像处理系统所需的内存空间,而且其最高时钟可达167MHz,峰值性能可达1600MIPS(百万条指令/秒)、2400MOPS(百万次操作/秒)。② 并行处理结构。TMS320C6211芯片内有8个并行处理单元,分为相同的两组,并行结构突破传统设计使得芯片具有很高的性能。③ 芯片体系采用VelociTI结构。VelociTI是一种高性能的甚长指令字(VLIW)结构,单指令字字长为32bit,8个指令组成一个指令包,总字长为256bit,即每秒钟可以执行8条指令,同时芯片内部设置了专门的指令分配模块,可以将每个256bits的指令包同时分配到8个处理单元,并由8个单元同时执行。④ 采用流水线操作实现高速度、高效率。TMS320C6211只有在流水线充分发挥作用的情况下,才能达到最高的MIPS。C6211的流水线分为3个阶段:指令读入、解码和执行,总共11级。

评论