PCI总线数据采集系统的硬件研究

引言

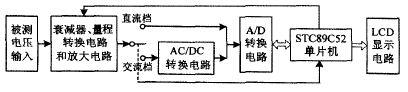

数据采集是指将温度、压力、流量、位移等模拟量采集并转换成数字量的过程。随着当今社会科学技术的15I速发展。数据采集已经广泛地应用于我们的生产生活中。从工业生产中普遍应用的自动控制系统到医疗设备中的各种测量监控仪器,从航空航天中的卫星遥感技术到军事科技中的制导技术,从当今可部分替代人类的机器人到日常生活中小小的数字体温计,无不存在数据采集的身影。南此可见,数据采集在整个系统中占有重要作用,数据采集的质量直接关系到整个系统的指标,因此对数据采集的研究具有重要意义。

1 TMS320VC5402的主机接口(HPI)

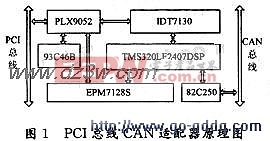

目前一般的DSP运算速度为100MIPS,即每秒钟可运算1亿条指令,但仍嫌不够快。由于电子设备的个人化和客户化趋势,DSP必须追求更高更快的运算速度,才能跟上电子设备的更新步伐。DSP运算速度的提高,主要依靠新工艺改进芯片结构。目前,TI的TM320C6X芯片由于采用 VLIW(VerylJ0nglnstmctionWord超长指令字)结构设计,其处理速度已高达2000 MIPS。当前DSP器件大都采用0.5~0.35IxmCMOS工艺,按照CMOS的发展趋势,DSP的运算速度再提高100倍(达到1600 GIIX5)是完全有可能的。TMS320C5402DSP性能强大,通用性强,接口方便,综合多方面考虑,决定选择它作为MCUtlI,C5402拥有改良的增强型的HPI,如图l所示。HPI是主机与C5402进行数据交换的8-bit并行数据口。该接口在C5402芯片上,内部有HPI数据寄存器,控制寄存器。HPI是用8-bit的数据线传输16_bit的数据,可通过设置控制寄存器的相关位控制高8位和低8位的传输。

增强型HPI采用共用访问模式(SAM),这是常用的模式。主机和DSP都能访问HPI存储器(二者产生冲突时,主机有较高的优先权),而异步的主机访问可以在HPI内部重新得到同步。HPl支持主机与DSP之间高速传输数据。sAM模式下,DSP运行在40MHz CLKOUT时,HPI每经过5个CLKOUT周期传输一个字节,即64M从,对于40MHz的DSP(外部访问周期为4),主机可以运行在30 MHz的速度下,而不需插入等待状态。

1.1 HPI主要组成部分

(1)HPI存储器(DRAM)。HPI RAM主要用于C54x与主机之间传送数据,5402片上有1个16K字x16位的DARAM作为HPI存储器。

(2)HPI地址寄存-器-(I-tPIA)。它只能由主机对其直接访问。寄存器中存放当前寻址HPI存储单元的地址。

(3)HPI数据锁存器r(HPID)。它也只能由主机对其直访问。如果当前进行的是读操作,则HPID中存放的是要从HPI存储器中读出的数据;如果当前进行的是写操作,则HPID中存放的是将要写到HPI存储器的数据.

(4)HPI控制寄存器(HPIC)。可以由主机或5402直接访问,包含了HPI操作的控制和状态信息。

1.2 HPI工作原理

HPI一8的使用是通过对HPIA,HPIC和HPID三个寄存器赋值实现的。简单地说,HOST通过外部引脚HC—NTL0和HCNTLl选中不同的寄存器,则当前发送的8位数据就送到该寄存器,HPI时序如图2所示。

在使用上,由于HPIC是16位寄存器,而HPI一8是8位的数据宽度,所以在HOST向HPIC写数据时,需要发送2个相同的8位数据。而地址寄存器 HPIA选择后,直接向它写数据即可以,但是要注意MSB和LSB的顺序。另外,HPIA具有自动增长的功能,在每写入1个数据前和每写入1个数据后,HPIA会自动加l。这样,如果使用了该功能,只需设定1次HPIA即可实现连续数据块的写入和读出。数据寄存器HPID,严格说应该叫做数据缓冲寄存器,因为最终数据是要写到片内RAM的。只是在实现上,数据首先从HOST发到HPID中,然后根据HPIA指定的地址,HPID中的数据再写到片内 RAM的地址中。不过对用户而言,该过程是透明的.

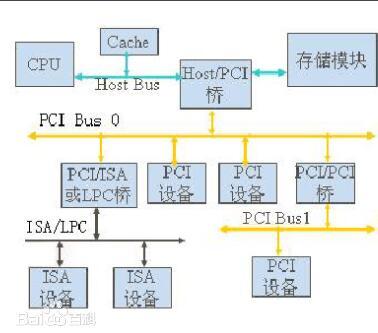

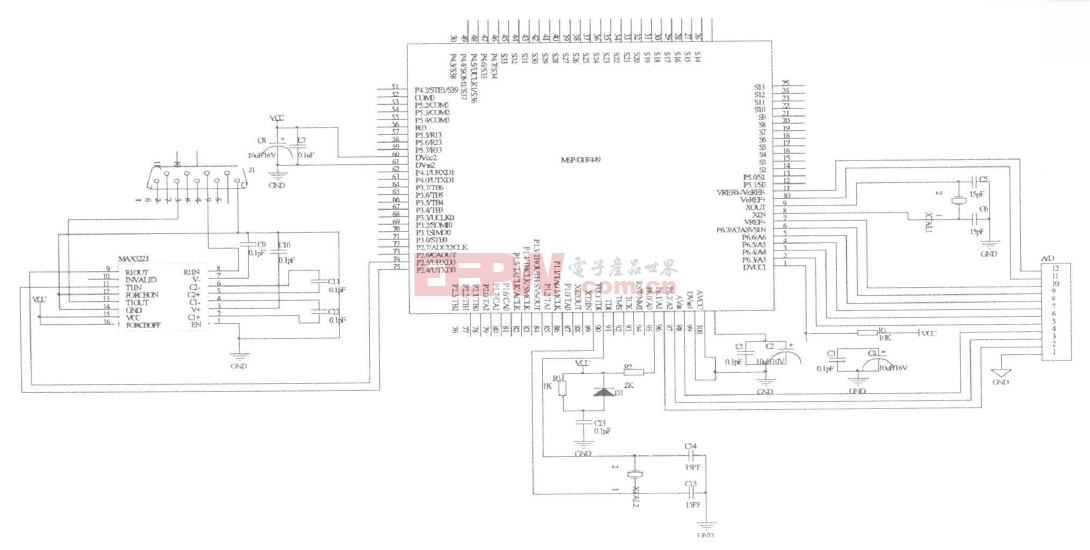

2 PCI9052与TM$320VC5402的接口

PCI9052的局部总线设置为8位局部总线,采用地址数据非复用模式翩。此时,/LBEl为LAl,/LBEO为LAO。将LBEO接HPI的 HBIL,用以区分第一字节和第二字节。LAl7接C5402的HCNTLl,LAl6接HCNTLO,以选择HPI寄存器。如图3所示,PCI 9052的LAD[ft.7】连C5402的HDr7删;5402的/HINT反相后接到PCI9052的LINTl,之所以反相是由于/HINT是低电平有效,而LINTl是高电平有效。PCI9052的LW/R反相后接到5402的HR/W,因为Lw/R高电平表示写,低电平表示读;而HR/W高电平表示主机要读HPI,低电平表示主机要写HPI;PCI9052的CS0,CSl相或连接到/HCSmD和/WR分别接到/HDSl,/HDS2;5402的/HRDY通过一定的逻辑组合再加上1个D触发器与9052的/LRDY相连接以实现9052与HPI的同步。 PCI9052局部时钟采用40MH。

CPLD采用EPM7128芯片,使用MAX+plusII进行设。其设计的过程包括4个阶段,设计输入、设计处理、设计校验和器件编程。 MAX+plus II软件的设计输入方法有很多,主要包括原理图输入方式、文本设计输入方式、高级设.计输入方式、波形设计输入方式、层次设计输人方式和底层设计输入方式.

3 AD转换芯片与TMS320VC5402接口

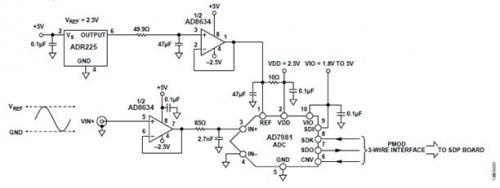

AD转换器采用TI公司的TLC5510芯片,它为8bit,20Msps的高速并行AD转换器。TLC5510在每个时钟的下降沿时进行采样。该采样点的转换数据经过2.5个时钟延迟后,在时钟的上升沿时输出,也就是每个点的转换时间为2.5个时钟周期,一旦转换流水线启动,则在每个时钟的上升沿都有一个点的转换数据输出。TIE5510时序转换图,如图4所示。

使用内部产生的基准电压,将模拟输入定为5 V,则参考低电压设定为0.6 V,参考高电压设定为2.6 V,这样满量程为2v,当输入电压为0.6V时,AD转换的数据为O,当输入电压为2.6 V时,AD转换的数据为255。

TI_E5510的输出D1一D8通过SN74LV245缓冲后接到DSP的IMI--D7,TLC5510输出使能接地。SN74LV245输出使能接 DSP的/IS,即将DSP的10空间全部分配给TLC5510,如果还有其它IO设备,可用地址译码实现。时钟输入采用DSP定时器TOUT输出。 TLC55 10接口。

4端口映射

HPI主机接口采用访问寄存器的方式来进行DSP内部数据的读写,把HPI口单纯映射到PCI的I/O空间或者存储器空间,都有不可避免的缺点,因此该接口电路采用双映射方式,利用I/O映射来访问控制、地址寄存器和单个数据口,而用存储器映射来访问连续数据口,以实现5402与PCI9052之间方便、高效的数据通信。这也PCI9052使用了2个片选信号的原因。

评论