基于Actel反熔丝FPGA的高速DDR接口设计

1. 3 高速接口方案设计

本应用目标对FPGA 和DAC 之间的高速接口提出如下要求:

( a) DAC 输出1 路115MHz 时钟给FPGA;( b ) FPGA 输出1 路115MHz 时钟和2 路230Mbps 数据给每片DAC.

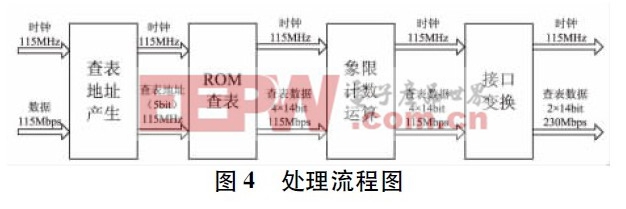

针对这一需求,考虑到FPGA 资源余量较大,为了降低系统运行速率,程序设计中遵循了用面积换取速度的原则,先采用115MHz 时钟进行并行处理,产生4 路115Mbps 的14bit 量化数据,在输出接口处将其转换为2 路230Mbps 的14bit 量化数据,这样可以使系统时钟的速率降低一半。处理流程如图4 所示。

输出端接口变换部分是我们讨论的重点,它对数据进行4 路到2 路的转换,量化数据从115Mbps提高到230Mbps,有2 种方式可以实现:

方式一: 对输入115MHz 时钟进行2 倍频得到230MHz 时钟,使用异步FIFO 对数据进行4 路写入,2 路读出,写钟为115MHz,读钟为230MHz.

方式二: 将4 路14bit 的量化数据分为2 组,每一组均使用115MHz 时钟进行DDR 输出接口处理,从而使每一组的输出均达到230MHz.

下面对2 种方式的可行性进行分析。

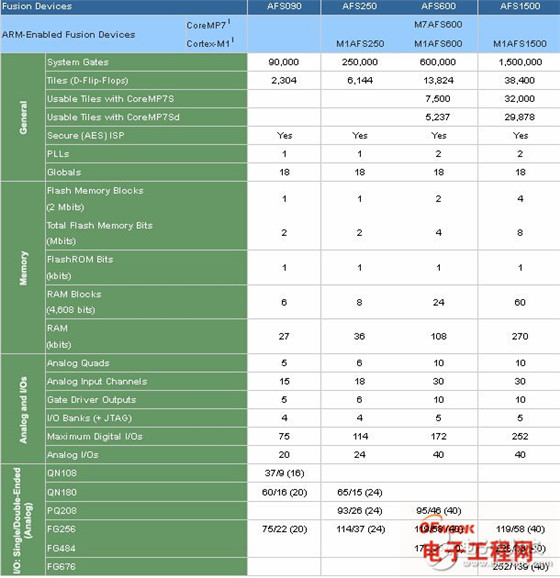

对于方式一,实现的关键在于2 倍频时钟的产生。按照手册描述,Actel 公司AX 系列芯片作为反熔丝FPGA 中处理能力最强的器件,内部处理时钟最高可以达到350MHz,且芯片内部集成了PLL( 延迟锁相环) 资源,可以实现对数字时钟信号的倍频和分频。而选择RTAX-S 系列在AX 的基础上进行了耐辐射能力加强,同时去掉了PLL 资源,原因是Actel公司通过实验证明PLL 资源在空间环境中使用是不可靠的,这意味着倍频无法在FPGA 内部实现。

因此,如果采用方式一,需要在FPGA 外部增加一个2 倍频的器件,还要增加相应的电平匹配的电路,这一切对于230MHz 的数字时钟信号实现上难度较大。

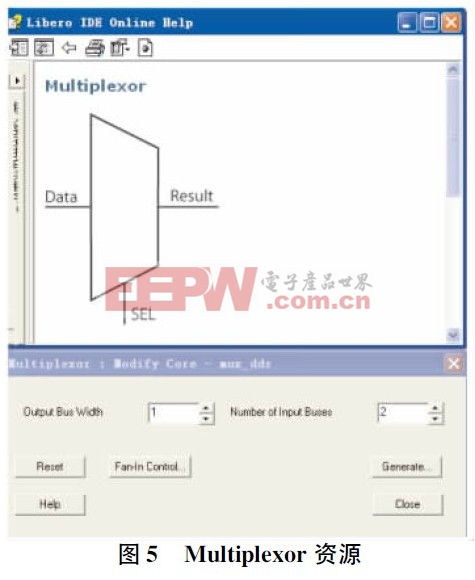

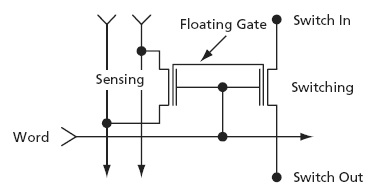

对于方式二,实现的关键在于DDR 输出。通过查阅器件手册可知,Actel 公司的RTAX – S 系列与Xilinx 公司SRAM 型FPGA 不同,其内部并没有现成的DDR 输出模块可以调用,但是其内部有一种叫做Multiplexor 的多路选择器资源,可以实现多路输入到多路输出的选择控制,如图5 所示。

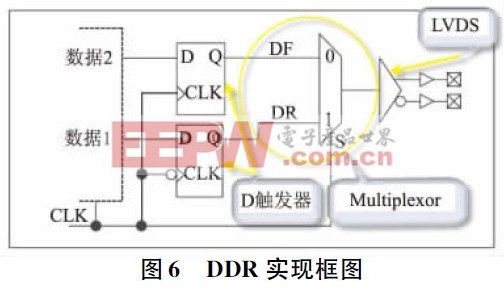

如果将其输入Data 设置为2 路,输出Result 设置为1 路,而时钟作为控制信号SEL,则应当可以实现DDR 的效果。具体实现框图如图6 所示。

图6 框图实现的时序如图7 所示,从图7 可以看出两路数据在DDR 变换后交替输出,速率提高一倍,其中DR( 数据1) 先输出,DF( 数据2) 后输出。

评论