基于Actel反熔丝FPGA的高速DDR接口设计

0 引言

随着航天技术的发展,FPGA 等大规模逻辑器件越来越成为不可缺的角色; 同时处理数据量的增大、以及各类型接口电路的交叉使用,使得合理、可靠的高速接口设计成为衡量设计优劣的关键。而由于空间环境的特殊性,导致近年来在轨卫星产品中单粒子翻转( SEU) 频发,使得设计人员必须考虑将以SRAM 为基础的FPGA 设计移植到更为可靠的ASIC或反熔丝FPGA.

DDR( Double DataRate) 是双倍速率读写技术的意思。传统的数据处理方式在1 个时钟周期内只传输1 次数据,是在时钟的上升期进行数据传输; 而DDR 内存则是1 个时钟周期内传输2 次数据,能够在时钟的上升期和下降期各传输1 次数据,因此称为双倍速率读写技术。采用DDR 技术可以在相同的总线频率下达到更高的数据传输率。

文章根据实际的背景应用提出一种基于Actel公司RTAX-S 系列耐辐射反熔丝FPGA 芯片RTAX250S 的高速DDR 接口设计方法,并通过Actel公司IDE V9. 0 编译软件和Modelsim 6. 5d 仿真软件进行了仿真验证。该方法已用在某星载GMSK 调制器上,获得了良好的效果。

1 DDR 高速接口设计

1. 1 RTAX – S 系列反熔丝FPGA 的特点

对于卫星应用,设计人员在选择可选的技术时一向十分为难。在可编程器件领域,其中就包括了专用集成电路( ASIC) 、以SRAM 为基础的现场可编程门阵列FPGA 和以反熔丝为基础的FPGA.由于没有一种技术是万能的,卫星设计人员与所有设计人员一样面对同样的挑战,需要针对特定的应用权衡取舍各种特性以找出最佳方案。

以往的设计中,以SRAM 为基础的FPGA ( 以Xilinx 产品为代表) 有着更多的应用,其优势在于拥有高逻辑密度和高灵活性,而作为航天应用,其致命的缺点是所有SRAM 都易受高强度宇宙辐射所影响,来自宇宙射线中的重离子很容易在SRAM 单元中或附近沉积足够的电荷导致单一数据位出错即单粒子翻转( SEU) ,而且由于SRAM 型FPGA 在SRAM开关中存储其逻辑配置,因此很容易出现配置扰乱导致电路的布局和功能受到破坏,这些错误非常难以检测和纠正,并且几乎不可能预防,因为配置开关在SRAM FPGA 的整个SRAM 数据位中超过90% ,辐射诱发的配置扰乱可导致系统失效。

对于卫星设备,ASIC 是具有最高密度最小重量和最低功耗的解决方案,然而却缺乏FPGA 所提供的灵活性。而且当把设计工具成本、校验时间和非经常性工程费用( NRE) 一并考虑之后,ASIC 也是成本较高的解决方案。

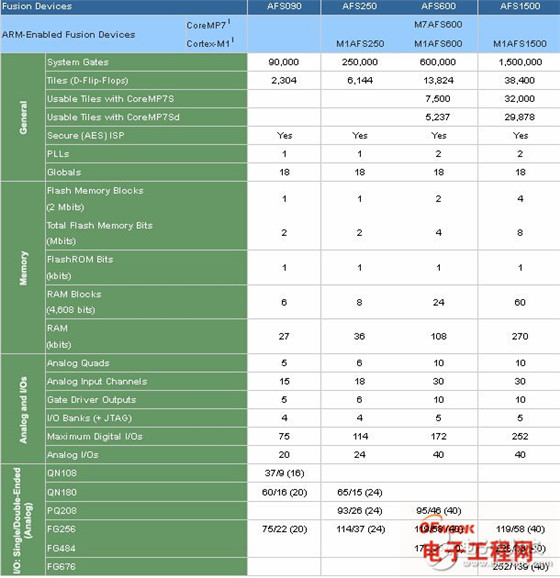

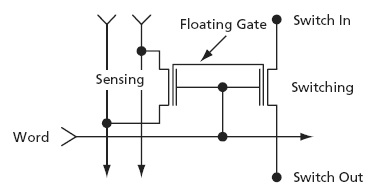

与可重新配置的SRAM 型FPGA 不同,基于反熔丝解决方案的FPGA 采用一次性编程( OTP) .其优点为固有的非挥发性以及在每次启动时无须进行强制性的器件配置。与ASIC 一样,反熔丝FPGA 的上电即行功能使其成为真正的单芯片解决方案。在各种学术会议上已发表了许多辐射测试数据,如IEEE 的核空间辐射影响会议( NSREC) 、NASA 的军事和航天可编程逻辑器件国际会议( MAPLD) ,事实上,多年的测试证明,耐辐射的反熔丝FPGA 具有SEU 免疫力,其性能也不会因TID( 总电离剂量) 随时间积累而发生劣化。众所周知,逻辑触发器中的数据易被宇宙辐射线所破坏,与SRAM 方案采用软TMR( 三模冗余) 方法不同,Actel 开发的耐辐射反熔丝FPGA RTAX-S 系列通过架构的提升解决了这个问题,其中每个触发器实际上是由3 个触发器和1个表决电路组成,此举可让设计人员获得优于63MeV-cm2 /mg 的LETth,可以满足大多卫星项目的TID 要求。

1. 2 典型高速接口电路应用目标

文章中高速接口方案的应用目标为GMSK 调制器中基带数据的数字高斯滤波。

GMSK 调制是一种典型的恒包络数字调制技术,实现方法的流程图如图1 所示,一路待调制的基带数据从A 处进入FPGA,FPGA 内部通过查表的方式得到量化后的波形数据,并分别从B 处和C 处将其送给2 片DAC,得到需要的I、Q 路波形,从而完成基带数据的数字高斯滤波。

硬件电路的关键是高速DAC 器件的选择。方案中需要DAC 实现4 倍采样,即图1 中A 处每输入1 个码元,B 处和C 处都要分别产生4 个点的量化信息给DAC.以115Mbps 码速率为例,DAC 的采样时钟应当为115MHz × 4 = 460MHz,如果使用传统的单路DAC,则FPGA 主时钟工作在460MHz,目前宇航级FPGA 无法满足这一速率。方案中选择了TI 公司最新的高速DAC 产品DAC5670,它在最高采样频率达到2.4GHz 的同时,内部集成了并串转换模块,这使得FPGA 的处理速率至少可以降低一半,即230MHz.

图1 应用目标实现流程图DAC5670

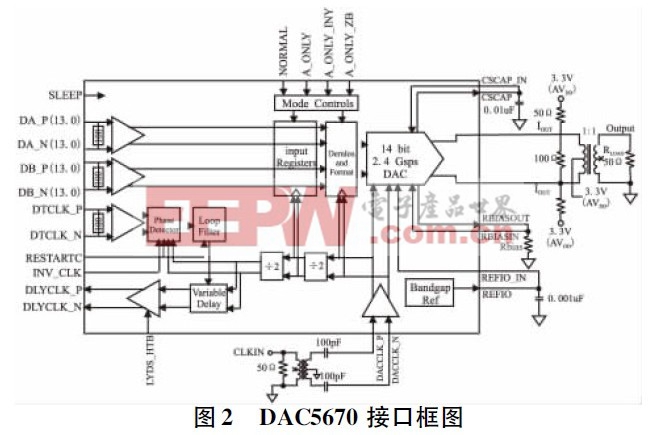

DAC5670 器件手册推荐的接口框图如图2 所示。

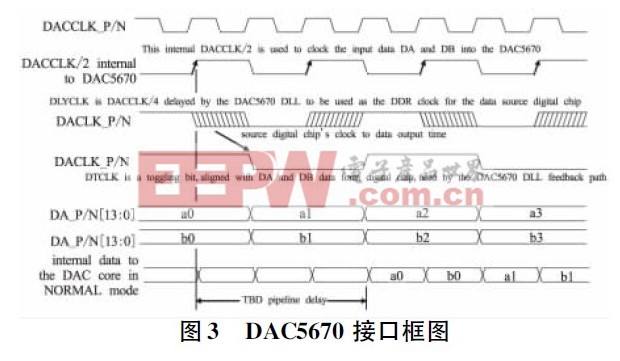

器件工作原理如下: 频率源输出400MHz 采样时钟,通过变压器进行单端转差分输入DAC 采样钟输入口( DACCLK) ,DAC 内部进行2 级2 分频并延迟后得到LVDS 电平115MHz 时钟( DLYCLK) 输出给FPGA 做数字处理,FPGA 处理完成后输出LVDS的100MHz1 路时钟( DTCLK) 和2 路14bit 的量化数据( DA( 13: 0) 和DB( 13: 0) ) .时钟与数据的关系必须满足图3 所示的时序。DAC 内部的锁相电路将DTCLK 与器件内部的100MHz 进行鉴相,如果存在相差则调整DLYCLK 的延迟量,直到同步,从而保证采样钟DACCLK 能够对DA( 13: 0) 和DB( 13: 0) 进行正确采样。

评论