一种基于FPGA的SOC设计方案

为减少在印制电路板(PCB)设计中的面积开销,介绍一种Flash结构的现 场可编程门阵列(FPGA)器件,进而介绍采用该器件搭建基于先进精简指令集机器(ARM)的片上系统(SOC)电路的设计方法,该方法按照高级微控制器总线架构(AMBA),设计ARM7处理器微系统及其外设电路,通过用搭建的系统对片外存储器进行擦写,以及通过编写软硬件代码定制符合ARM7外围低速总线协议的用户逻辑外设,验证了系统的准确性,该系统可用于验证SOC设计系统。

本文引用地址:http://www.eepw.com.cn/article/262872.htm近年来,SOC技术得到了快速的发展,逐渐 成为微电子行业的主流。SOC称为系统级芯片,是一个有专用目标的集成电路,能集成数字电路、硬件专用电路、存储器、微处理器等多种异构模块,实现多个复杂的应用功能,具有速度快、集成度高、功耗低、开发周期短等优点。

随着集成电路速度的加快和设计复杂性提高,新的技术不断被引进,国内外相继开展了SOC技术及器件的研究,其中一个显着的特点就是将SOC的可靠性和低成本与FPGA的灵活性等优势结合起来,在业界中知名的FPGA芯片公司中,如Ahera公司的Cyclone V和A1Tia V系列引,Xilinx公司的Zynp系列,Actel公司的M7A3P1000,其都内嵌了ARM微处理器,在逻辑设计、片上系统中都有广泛的应用。

本文选用Actel公司的FPGA器件,型号为M7A3P1000,采用该器件对SOC进行设计验证。该器件采用Flash结构,相比于采用静态随机存储器(SRAM)结构的Ahera和Xilinx公司的FPGA器件,其下载的程序在掉电后不丢失,因此不需专用的配置芯片,故在PCB设计中可降低设计的复杂度,减少面积的开销。此外,该器件所具有的的 加密功能,可有效的保护知识产权。设计中,首先在该芯片中搭建基于ARM7的SOC系统,最后用两种方法验证该SOC系统的正确性:一是用该系统对片外存储器进行擦写操作;二是用该系统测试用户定制逻辑外设。

1 系统原理

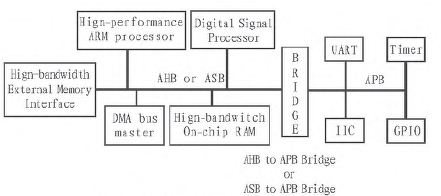

在SOC设计中,常见的架构都是以微处理器或数字信号处理器(DSP)为中心,加上存储器,外设等,再通过片上总线把处理器和外设进行互连,本设计采用的FPGA型号为M7A3P1000芯片,因其内嵌一个基于AMBA总线架构、且完全兼容ARM7微处理器,故可以在非常低的功耗下安全、可靠地运行。上述的AMBA总线架构,是ARM公司设计的一种高性能嵌入式系统总线的标准,因其具有的高速度、低功耗等特点,故其在SOC设计中已被广泛采用,典型的基于AMBA架构的SOC核心部分如图1。

由图1中可看出,AMBA规范中定义了两种不同类型的总线:先进的高速总线(AHB)、先进的系统总线 (ASB)和先进的外围总线(APB)。其中AHB适用于高性能和高时钟频率的系统模块,主要用于高性能和高吞吐量设备之间的连接,如片上存储器、DSP、直接存储器访问(OMA)、高速片外存储器控制器(该部件用于连接片外存储器Flash和SRAM)等设备;ASB和AHB属同一功能类型总线,只不过AHB总线是ASB总线的升级版,增强了对性能、综合及时序验证的支持;APB总线主要用于连接低速、低带宽的外围器件,如集成电路总线(IIC)接口、计数器(Timer),通用输入输出(GPIO)、通用异步收发器(UART)等。下文将以此架构,进行SOC设计。

图1 AMBA架构的SOC核心部分

2 系统设计

2.1 SOC设计流程

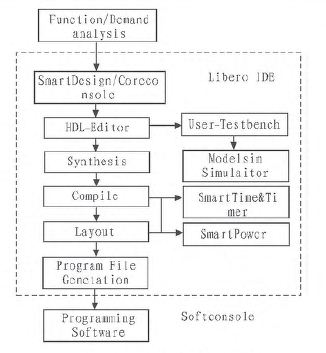

采用Aetel公司的Libero IDE 8.6集成开发环境,设计基于ARM7的SOC.SOC包括硬件和软件设计两部分,在硬件设计中,一般将系统经行分模块设计,之后针对各模块功能,逐个进行功能验证,待各模块功能准确后,依据总线架构,组成要设计的目标系统,最后通过软硬件协同调试,证明系统功能的完备性。其SOC设计的主要流程如图2。

在图2显示的SOC设计流程中,若要设计一个模块或系统,首先对其进行功能/需求分析,下来针对虚线 框内的步骤, 其中步骤HDL-Editor,User-Testbeneh.ModelsimSimulator,可用于模块的设计、功能仿真,若再增加步骤Synthesis,Compile,Layout,Programming Genetation,可对所设计的模块进行实际验证,待各模块功能验证准确后,就可以依据指定的互连结构组成系统,然后结合相应的软件代码,进行系统功能调试、验证。

图2 SOC设计的主要流程

2.2 SoC设计搭建

本文采用在Libero IDE 8.6集成开发环境中内嵌的Coreconsole软件8,搭建基于ARM7的SOC系统,搭建的系统如图3所示。

图3 基于ARM7的SOC系统

如图3所示,在Coreeonsole环境中搭建的系统,包括总线,微处理器,外围器件,以及驱动和顶层端口,其中1)CoreMP7:32/16位精简指令集架构处理器、支持32位ARM指令和16位Thumb指令、三级流水线,32位即4G寻址范围等;2)CoreMP7Bridge:桥接器,连接CoreMP7 和CoreAHB,它将CoreMP7处理器发出的信号转换成一个适合AHB总线连接的信号,且包含一组联合测试行动小组(JTAG)信号接口,JTAG接口用于下载程序和软件调试。3)CoreAHBLite:先进的高速总线,一般连接DMA、DSP、SRAM等设备。包含16个AHB从器件节点,每个从器件依次占有256MB地址空间,在本设计中,片外的Flash和SRAM分别连接在节点0和节点1上。2.1部分中用到的片外Flash就是通过外部存储器接口连接在节点0上,故其基地址是Ox00000000;4)CoreMemCtrl:外部存储器控制器,用于连接片上系统与外部寄存器,如对片外Flash、SRAM进行读写访问;5)CoreAHBtoAPB:桥接器。连接CoreAHB和CoreAPB;6)CoreAPB:先进的外围总线,一般连接UART、GPIO、IIC等外设。包含16个APB从器件节点,每个从器件依次占有16MB地址空间,地址计算公式是:物理地址=基地址+偏移地址。7)驱动和顶层端口包括:16 MHz系统时钟SYSCLK;系统低电平复位端口NSYSRESET,程序下载和调试端口JTAG,外部存储器连接端口ExtemalMomopyInterthce,串口通信接口等,图中底色为灰色的是一般的输入输出(PIO)模块,该模块的设计和验证将在3.2部分详细说明。至此,文中介绍了基于AMBA总线架构的SOC中涉及到的时钟、复位、总线、微处理器、外部存储器及外围输入输出端口,即最小系统框架,在图3中清晰地确定了SOC系统的互连结构,实现了各模块之间的通信功能。

3 实际验证

下面将对所搭建的SOC系统进行验证,通过对系统翻译、编译、综合、分配管脚、生成下载文件,最后将下载文件烧写到FPGA片中。为验证该系统的准确性,本设计采用两种方法对其进行测试验证,详细过程见3.1和3.2部分。

3.1 搭建的系统对片外Flash的擦写操作

本测试主要是在已经搭建好的SOC系统的基础上,在外部存储器控制器接口连接外部存储器Flash,通过能否对Flash进行正常的擦写操作来验证系统的准确性,测试选用的片外Flash芯片型号Numonyx公司是28F640J3D,它是64M的16位只读存储器,分配的基地址是Ox00000000,由于该芯片16位模式的访问特性,地址线0位拉低不予链接,其余地址线管脚依次连接到顶层外部寄存器控制器的地址端口。

FS2是一款集合了大量指令和可用软件、用以调试基于ARM的SOC系统内核的工具,利用该工具对片外Flash进行配置和擦写操作,来验证系统的准确性。测试首先对片外Flash进行配置,进而对指定存储空间进行擦除操作,然后对该存储空间进行写操作,最后观察此存储空间中的数据,具体过程如图4所示。

fpga相关文章:fpga是什么

存储器相关文章:存储器原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论