电路板级的电磁兼容设计

c)RC端接

图14演示了RC端接方法。这个方法类似于并联端接,但是增加了一个C1。和在并联端接方法中一样,R用于提供匹配Z0的阻抗。C1为R提供驱动电流并过滤掉从线迹到地的射频能量。因此,相比并联端接方法,RC端接方法需要的源驱动电流更少。R和C1的值由Z0,Tpd(环路传输延迟)和Cd确定。时间常数,RC = 3 x Tpd,这里R // ZL = Z0, C = C1 // Cd。

d)Thevenin端接

图15演示了Thevenin端接方法。此电路由上拉电阻R1和下拉电阻R2组成,这样就使逻辑高和逻辑低与目标负载相符。

R1和R2的值由R1 // R2 = Z0决定。R1 + R2 + ZL的值要保证最大电流不能超过源驱动电路容量。举例来说, R1=220欧,R2=330 欧

这里VCC是驱动电压

e)二极管端接 (Diode termination)

图16演示了二极管端接方法。除了电阻被二极管替换以降低损耗之外,它与Thevenin端接方法类似。D1和D2用来限制来自负载的过多信号反射量。与Thevenin端接方法不一样,二极管不会影响线性阻抗。对这种端接方法而言,选择Schottky和快速开关二极管是比较好的。这种端接方法的优点在于不用已知Z0的值,而且还可以和其他类型的端接方法结合使用。通常在MCU的内部应用这种端接方法来保护I/O端口。

• 微控制器电路

时下,许多IC制造业者不断地减小微控制器的尺寸以达到在单位硅片上增加更多部件的目的。通常减小尺寸会使晶体管更快。这样一来,虽然MCU时钟速率无法增加,但是上升和下降速度会增加,从而谐波分量使得频率值上升。许多情况下,减小微控制器尺寸无法通知给用户,这样最初时电路中的MCU是正常的,但以后在产品生命周期中的某个时间就可能出现EMC问题。对此最好的解决方法就是在开始设计电路时就设计一个较稳健的电路。许多实时应用方面都需要高速MCU,设计者一定要认真对待其电路设计和PCB布线以减少潜在的EMC问题。MCU需要的电源功率随着其处理功率的增加而增加。让供给电路(比如校准电路)靠近微控制器是不难办到的,再用一个独立的电容就可以减少直流电源对其它电路的影响。

MCU通常有一个片上振荡器,它用自己的晶体或谐振器连接,从而避免使用其他时钟驱动电路的时钟。这个独立的时钟能更好地防止系统其他部份所产生的噪声辐射。在时钟频率方面,MCU通常是对功率要求最高的设备,这样让时钟靠近MCU就能保证对时钟频率仅有最小的驱动需求。

1.I/O口引脚

对于大多数MCU,引脚常都是高阻输入或混合输入/输出。高阻输入引脚易受噪声影响,并且在非正常终端时会引至寄存器锁存错误的电平。一个非内部终端的输入引脚需要有高阻抗(例如4.7KΩ或10KΩ)连接每个引脚到地或者到供电电平,以便确保一个可知的逻辑状态。未连接的输入引脚通常浮动在供电电平的中间值周围,或者由于有内部泄露通路而浮动在不确定的电压值。

对于IRQ或复位引脚(输入引脚)来说,其终端比普通I/O口引脚更为重要。如果噪声导致这两个引脚误触发,它将对整个电路的行为产生巨大的影响。当输入引脚未连接,同时输入锁存器半开半闭时,会导致IC内部电流泄漏,此时通常可以看到高电流消耗,尤其是在CMOS器件中。因此在输入引脚终端连接高阻抗可以减少供电电流,就象电磁兼容的其他好处一样。

2.IRQ口引脚

由于中断对MCU操作有影响,因此它是元件中最敏感的引脚之一。从远端设备到PCB板上的MCU,甚至在插件适配器或子系统卡上,IRQ都可以被查询。因此,确保与中断请求引脚的任何连线都有瞬时静电释放保护是非常重要的。对于静电释放来说,在IRQ连线上有双向二极管、transorbs或金属氧化变阻器终端通常就足够了,而且他们还能在不产生大的线路负荷的情况下帮助减少过冲和阻尼震荡。即便是对价格很敏感的应用,IRQ线上的电阻终端也同样不可缺少。

3.复位引脚

不恰当的复位将导致许多问题,因为不同的应用利用了MCU启动和断电的不同条件。复位最基本的功能保证了一旦上电,MCU便开始用可控制的方式执行代码。上电时,电源上升到MCU的工作电压,在晶振稳定之前需要等一段时间。因此在复位引脚上要有时间延时。最简单的延时就是电阻-电容(RC)网络,在电流经过电阻时电容开始充电,一直到电平达到了能被MCU在逻辑1状态时的复位电路检测到的值为止。理想情况下没有严格规定电阻和电容的大小,但也有其他方面的考虑。复位引脚的内部泄漏电流通常规定不能超出1µA(针对 Motorola HC08 MCU),这意味着电阻最大为100kΩ,电容不能是电解电容,以保持停止电流的最小值。推荐使用陶瓷电容,因为它折衷了低价格,低泄漏,高频反应性能好的优点。复位引脚电容非常小(Motorola HC08 MCU 低于5pF)。对于最小阻抗值也有限制,因为最大上拉电流大约为5mA,1V (VOL)。加上外部电容的低阻抗电压源,则确定了上拉电阻的最小值为2KΩ。用二极管来钳住复位引脚的电压也是一种推荐做法,能防止供电电压过度,并且能够在断电时令电容迅速放电。

4.振荡器

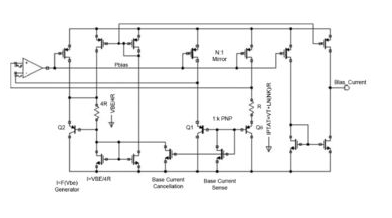

许多MCU合成了倒相放大器,用来与外部晶体或陶瓷共振器一起构成皮尔斯振荡器结构。下面则讨论用来与特殊外部元件一起得到振荡的放大器最小增益(跨导)。图17给出了MCU上使用的典型标准皮尔斯振荡器结构,晶体在1MHz到20MHz的频率范围。下面用简单的形式给出了MCU的内部电路,与非门后面是变极器。与非门有两个输入:一个连到MCU的OSC1脚,另一个连接到内部STOP上。

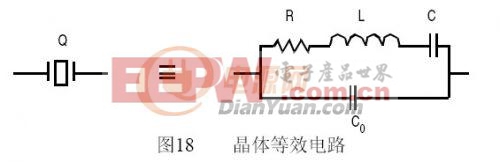

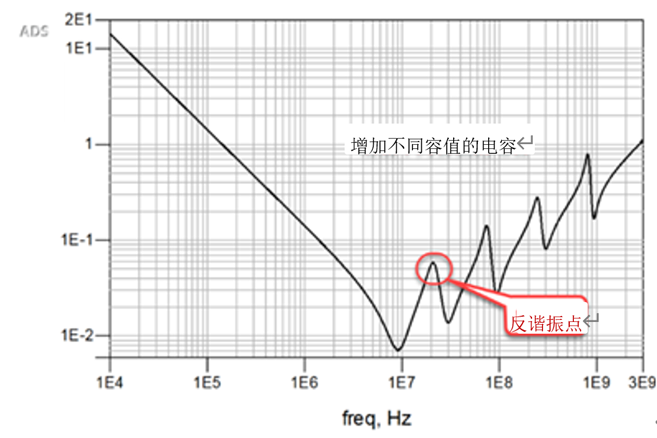

对于振荡电路来说,必须有正反馈,且闭环增益必须比1大。电阻R0导致了负反馈,增大了放大器的开环增益需求。R0通常尽量的大,以将反馈减到最小,同时克服上电时的电流泄漏。当使用1MHz和20MHz的晶体时,R0应该在1MΩ至10MΩ的范围里。对于陶瓷共振器,R0一般用1 MΩ。共振器Q和电容C1、C2构成了共鸣回路。C1、C2代表了外部电容和任何并行的寄生电容。晶体和陶瓷共振器有小信号等效电路,如图18所示:

R是串联电阻,L和C是起动或串联电感、电容。C0是分流电容,它代表了晶体盒中共振器和寄生电容的低频并联电容量的总和。任何在OSC1和OSC2引脚之间的附加寄生电容都包括在这个值里。晶体制造商的数据手册里详细说明了特殊晶体中R, L, C和C0的值。为了测量这些值,制造商必须给晶体送信号,也就是从晶体里功率消耗的特殊电平中获得。然而,在晶体启动时,通过晶体的唯一信号应归于热噪声,因此晶体里的功率消耗是非常低的。众所周知

,当晶体内功率消耗减少到低水平时R的有效值可以增长。因此R的最大值由晶体制造者来估计。既然R0, C1和C2的值不仅依赖于MCU的变极器特性,还依赖于外部晶体或陶瓷共振器的特性,则从各制造商的数据手册里可以得到精确的元件结构。

第三部分 — 印制电路板的布线技术

除了元器件的选择和电路设计之外,良好的印制电路板(PCB)布线在电磁兼容性中也是一个非常重要的因素。既然PCB是系统的固有成分,在PCB布线中增强电磁兼容性不会给产品的最终完成带来附

评论