电路板级的电磁兼容设计

对闭环电感来说,磁场被完全控制在磁心,因此在电路设计中这种类型的电感更理想,当然它们也比较昂贵。螺旋环状的闭环电感的一个优点是:它不仅将磁环控制在磁心,还可以自行消除所有外来的附带场辐射。电感的磁芯材料主要有两种类型:铁和铁氧体。铁磁芯电感用于低频场合(几十KHz),而铁氧体磁芯电感用于高频场合(到MHz)。因此铁氧体磁芯电感更适合于EMC应用。

在EMC应用中特别使用了两种特殊的电感类型:铁氧体磁珠和铁氧体磁夹。

铁和铁氧体可作电感磁芯骨架。铁芯电感常应用于低频场合(几十KHz),而铁氧体芯电感常应用于高频场合(MHz)。所以铁氧芯感应体更适合于EMC应用。在EMC的特殊应用中,有两类特殊的电感:铁氧体磁珠和铁氧体夹。铁氧体磁珠是单环电感,通常单股导线穿过铁氧体型材而形成单环。这种器件在高频范围的衰减为10dB,而直流的衰减量很小。类似铁氧体磁珠,铁氧体夹在高达MHz的频率范围内的共模(CM)和差模(DM)的衰减均可达到10dB至20dB。

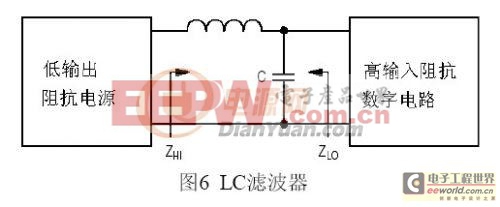

在DC-DC变换中,电感必须能够承受高饱和电流,并且辐射小。线轴式电感具有满足该应用要求的特性。在低阻抗的电源和高阻抗的数字电路之间,需要LC滤波器,以保证电源电路的阻抗匹配,如图6所示。

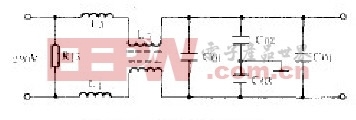

电感最广泛的应用之一是用于交流电源滤波器,如图7所示。

图7中,L1是共模扼流圈,它既通过其初级电感线圈实现差分滤波,又通过其次级电感线圈实现共模滤波。L1、CX1和CX2构成差分滤波网络,以滤除进线间的噪声。L1、CY1和CY2构成共模滤波网络,以减小接线回路噪声和大地的电位差。对于50Ω的终端阻抗,典型的EMI滤波器在差分模式能降低50 dB/十倍频程,而在共模降低为40 dB/十倍频程。

4.二极管

二极管是最简单的半导体器件。由于其独特的特性,某些二极管有助于解决并防止与EMC相关的一些问题。表2列出了典型的二极管。

二极管的应用

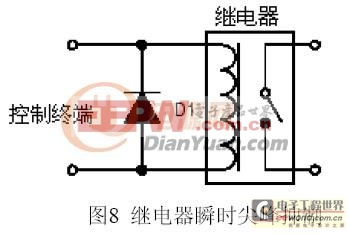

许多电路为感性负载,在高速开关电流的作用下,系统中产生瞬态尖峰电流。二极管是抑制尖峰电压噪声源的最有效的器件之一。下面举例说明用二极管实现尖峰抑制。

如图8所示,控制终端开/关线圈,线圈中的开关尖峰脉冲将耦合并辐射到电路的其它部分。二极管D1能嵌位电压的波动。

图9中的二极管用于抑制高压开关的尖峰电压。

图10是典型的变压和整流电路。D2是肖特基或齐纳二极管,用于抑制滤波后的尖峰瞬态噪声电压。

在汽车控制应用中,无论有刷还是无刷电机,当电机运行时,都将产生电刷噪声或换向噪声。因此需要噪声抑制二极管,为了改进噪声抑制效果,二极管应尽量靠近电机接点。在电源输入电路中,需要用TVS或高电压变阻器进行噪声抑制。信号连接接口的EMI问题之一是静电释放(ESD)。屏蔽电缆和连接器用于保护而不受外界静电的干扰。另一种方法是使用TVS或变阻器保护信号线。

• 集成电路

现代数字集成电路(IC)主要使用CMOS工艺制造。CMOS器件的静态功耗很低,但是在高速开关的情况下,CMOS器件需要电源提供瞬时功率,高速CMOS器件的动态功率要求超过同类双极性器件。因此必须对这些器件加去耦电容以满足瞬时功率要求。

1.集成电路封装

现在集成电路有多种封装结构,对于分离元件,引脚越短,EMI问题越小。因为表贴器件有更小的安装面积和更低的安装位置,因此有更好的EMC性能,因此应首选表贴器件。甚至直接在PCB板上安装裸片。IC的引脚排列也会影响EMC性能。电源线从模块中心连到I.C.引脚越短,它的等效电感越少。因此VCC与GND之间的去耦电容越近越有效。

无论是集成电路、PCB板还是整个系统,时钟电路是影响EMC性能的主要因素。集成电路的大部分噪声都与时钟频率及其多次谐波有关。因此无论电路设计还是PCB设计都应该考虑时钟电路以减低噪声。合理的地线、适当的去耦电容和旁路电容能减小辐射。用于时钟分配的高阻抗缓冲器也有助于减小时钟信号的反射和振荡。对于使用TTL和CMOS器件的混合逻辑电路,由于其不同的开关/保持时间,会产生时钟、有用信号和电源的谐波。为避免这些潜在的问题,最好使用同系列的逻辑器件。由于CMOS器件的门限宽,现在大多数设计者选用CMOS器件。由于制造工艺是CMOS工艺,因此微处理器的接口电路也优选这种器件。需要特别注意的是,未使用的CMOS引脚应该接地线或电源。在MCU电路中,噪声来自没连线/终端的输入,以至MCU执行错误的代码。它也是设计微控制器接口首选的逻辑系列产品,这些微控制器也是基于CMOS技术制造的。关于CMOS设备,一个重要方面就是其不用的输入引脚要悬空或者接地。在MCU电路中,噪声环境可能引起这些输入端运行混乱,还导致MCU运行乱码。

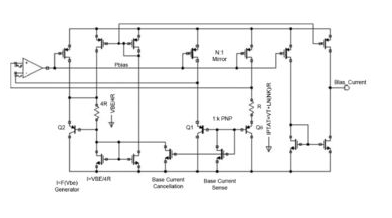

2.电压校准

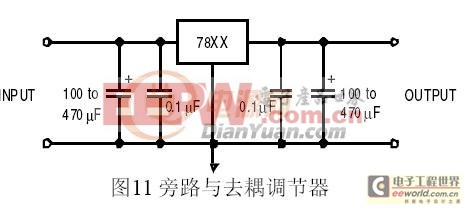

对于典型的校准电路,适当的去耦电容应该尽可能近地放置在校准电路的输出位置,因为在跟踪过程中,距离在校准的输出和负荷之间将会产生电感影响,并引起校准电路的内部振动。一个典型例子,在校准电路的输入和输出中,加上0.1uF的去耦电容可以避免可能的内在振动和过滤高频噪声。除此之外,为了减少输出脉动,要加上一个相对大的旁路电容(10uF/A)。图11演示了校准电路的旁路和去耦电容。电容要放到离校准装置尽可近的地方。

3.线路终端

当电路在高速运行时,在源和目的间的阻抗匹配非常重要。因为错误的匹配将会引起信号反馈和阻尼振荡。过量的射频能量将会辐射或影响到电路的其他部份,引起EMI(电磁兼容性)问题。信号的端接有助于减少这些非预计的结果。信号端接不但能减少在源和目的之间匹配阻抗的信号反馈和振铃,而且也能减缓信号边沿的快速上升和下降。有很多种信号端接的方法,每种方法都有其利弊。表3给出了一些信号端接方法的概要。

a) 串联/源端接 (Series/Source Termination)

图12演示了串联/源端接方法。在源Zs和分布式的线迹Zo之间,加上了源端接电阻Rs,用来完成阻抗匹配。Rs还能吸收负载的反馈。Rs必须离源驱动电路尽可能的近。Rs的值在等式Rs=(Z0-Zs)中是实数值。一般Rs大约取15-75欧的一个值。

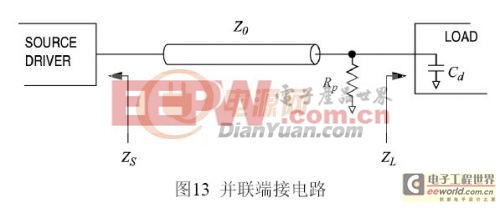

b)并联端接

图13 演示了并联端接方法。附加一个并联端接电阻Rp,这样 Rp/

评论