电路板级的电磁兼容设计

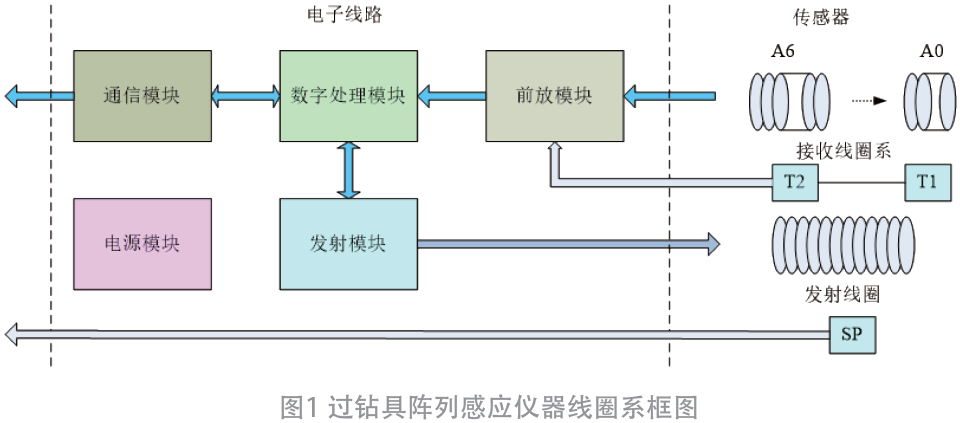

为了进行电磁兼容性设计并符合电磁兼容性标准,设计者需要将辐射(从产品中泄露的射频能量)减到最小,增强其对辐射(进入产品中的射频能量)的易感性和抗干扰能力。如图一所示,发射和抗干扰都可以根据辐射和传导的耦合来分类。辐射耦合在高频中十分常见,而传导耦合路径在低频中更为常见。

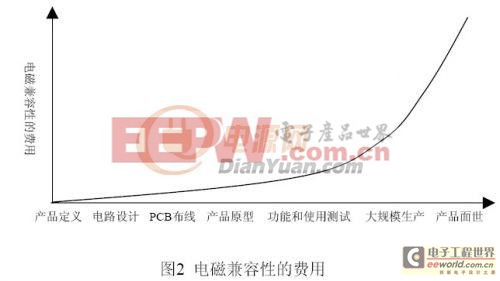

2. 电磁兼容性的费用

最经济有效的电磁兼容性设计方法,是在设计的早期阶段充分考虑评估电磁兼容性的技术要求(见图2)。

要让设计者在最初选择元件、设计电路和设计PCB布线时,就把电磁兼容性作为主要的设计依据是不大现实的。但是,如果设计者能牢记这篇文章的建议,那么,就能减少不合理的元件选择、电路设计和PCB布线的情况出现。

第二部分 — 元件的选择和电路设计技术

元件的选择和电路设计是影响板级电磁兼容性性能的主要因素。每一种电子元件都有它各自的特性,因此,要求在设计时仔细考虑。下面将讨论一些常见的用来减少或抑制电磁兼容性的电子元件和电路设计技术。

• 元件组

有两种基本的电子元件组:有引脚的和无引脚的元件。有引脚线元件有寄生效果,尤其在高频时。该引脚形成了一个小电感,大约是1nH/mm/引脚。引脚的末端也能产生一个小电容性的效应,大约有4pF。因此,引脚的长度

应尽可能的短。与有引脚的元件相比,无引脚且表面贴装的元件的寄生效果要小一些。其典型值为:0.5nH的寄生电感和约0.3pF的终端电容。从电磁兼容性的观点看,表面贴装元件效果最好,其次是放射状引脚元件,最后是轴向平行引脚的元件。

1.电阻

由于表面贴装元件具有低寄生参数的特点,因此,表面贴装电阻总是优于有引脚电阻。

对于有引脚的电阻,应首选碳膜电阻,其次是金属膜电阻,最后是线绕电阻。

由于在相对低的工作频率下(约MHz数量级),金属膜电阻是主要的寄生元件,因此其适合用于高功率密度或和高准确度的电路中。线绕电阻有很强的电感特性,因此在对频率敏感的应用中不能用它。它最适合用在大

功率处理的电路中。

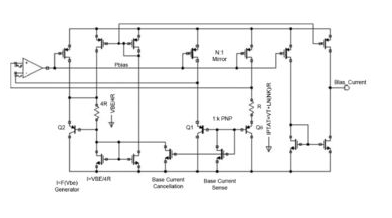

在放大器的设计中,电阻的选择非常重要。在高频环境下,电阻的阻抗会因为电阻的电感效应而增加。因此,增益控制电阻的位置应该尽可能的靠近放大器电路以减少电路板的电感。

在上拉/下拉电阻的电路中,晶体管或集成电路的快速切换会增加上升时间。为了减小这个影响,所有的偏置电阻必须尽可能靠近有源器件及他的电源和地,从而减少PCB连线的电感。在稳压(整流)或参考电路中,直流偏置电阻应尽可能地靠近有源器件以减轻去耦效应(即改善瞬态响应时间)。

在RC滤波网络中,线绕电阻的寄生电感很容易引起本机振荡,所以必须考虑由电阻引起的电感效应。

2.电容

由于电容种类繁多,性能各异,选择合适的电容并不容易。但是电容的使用可以解决许多EMC问题。接下来的几小节将描述几种最常见的电容类型、性能及使用方法。铝质电解电容通常是在绝缘薄层之间以螺旋状缠绕金属箔而制成,这样可在单位体积内得到较大的电容值,但也使得该部分的内部感抗增加。钽电容由一块带直板和引脚连接点的绝缘体制成,其内部感抗低于铝电解电容。陶质电容的结构是在陶瓷绝缘体中包含多个平行的金属片。其主要寄生为片结构的感抗,并且通常这将在低于MHz的区域造成阻抗。绝缘材料的不同频响特性意味着一种类型的电容会比另一种更适合于某种应用场合。铝电解电容和钽电解电容适用于低频终端,主要是存储器和低频滤波器领域。在中频范围内(从KHz到MHz),陶质电容比较适合,常用于去耦电路和高频滤波。特殊的低损耗(通常价格比较昂贵)陶质电容和云母电容适合于甚高频应用和微波电路。为得到最好的EMC特性,电容具有低的ESR(EquivalentSeries Resistance,等效串联电阻)值是很重要的,因为它会对信号造成大的衰减,特别是在应用频率接近电容谐振频率的场合。

a)旁路电容

旁路电容的主要功能是产生一个交流分路,从而消去进入易感区的那些不需要的能量。旁路电容一般作为高频旁路器件来减小对电源模块的瞬态电流需求。通常铝电解电容和钽电容比较适合作旁路电容,其电容值取决于PCB板上的瞬态电流需求,一般在10至470µF范围内。若PCB板上有许多集成电路、高速开关电路和具有长引线的电源,则应选择大容量的电容。

b)去耦电容

有源器件在开关时产生的高频开关噪声将沿着电源线传播。去耦电容的主要功能就是提供一个局部的直流电源给有源器件,以减少开关噪声在板上的传播和将噪声引导到地。实际上,旁路电容和去耦电容都应该尽可能放在靠近电源输入处以帮助滤除高频噪声。去耦电容的取值大约是旁路电容的1/100到1/1000。为了得到更好的EMC特性,去耦电容还应尽可能地靠近每个集成块(IC),因为布线阻抗将减小去耦电容的效力。陶瓷电容常被用来去耦,其值决定于最快信号的上升时间和下降时间。例如,对一个33MHz的时钟信号,可使用4.7nF到100nF的电容;对一个100MHz时钟信号,可使用10nF的电容。选择去耦电容时,除了考虑电容值外,ESR值也会影响去耦能力。为了去耦,应该选择ESR值低于1欧姆的电容。

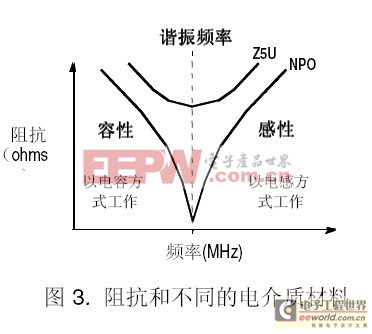

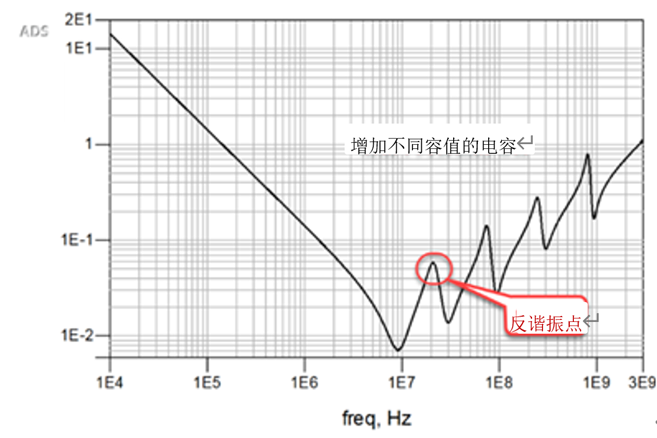

c)电容谐振

接下来简单讨论一下如何根据谐振频率选择旁路电容和去耦电容的值。如图3所示,电容在低于谐振频率时呈现容性,而后,电容将因为引线长度和布线自感呈现感性。表1列出了两种陶瓷电容的谐振频率,一种具有标准的0.25英寸的引脚和3.75nH的内部互连自感,另一种为表面贴装类型并具有1nH的内部自感。我们看到表面贴装类型的谐振频率是通孔插装类型的两倍。

另一个影响去耦效力的因素是电容的绝缘材料(电介质)。去耦电容的制造中常使用钡钛酸盐陶瓷(Z5U)和锶钛酸盐(NPO)这两种材料。Z5U具有较大的介电常数,谐振频率在1MHz到20MHz之间。NPO具有较低的介电常数,但谐振频率较高(大于10MHz)。因此Z5U更适合用作低频去耦,而NPO用作50MHz以上频率的去耦。

常用的做法是将两个去耦电容并联。这样可以在更宽的频谱分布范围内降低电源网络产生的开关噪声。多个去耦电容的并联能提供6dB增益以抑制有源器件开关造成的射频电流。

多个去耦电容不仅能提供更宽的频谱范围,而且能提供更宽的布线以减小引线自感,因此也就能更有效的改善去耦能力。两个电容的取值应相差两个数量级以提供更有效的去耦(如0.1 µF + 0.001 µF并联)。需要注意的是数字电路的去耦,低的ESR值比谐振频率更为重要,因为低的ESR值可以提供更低阻抗的到地通路,这样当超过谐振频率的电容呈现感性时仍能提供足够的去耦能力。

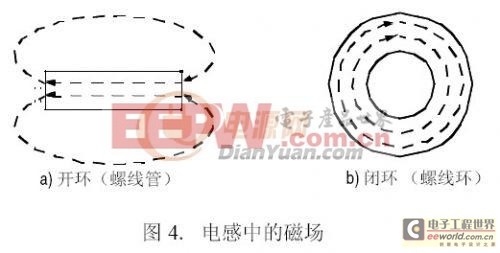

3.电感

电感是一种可以将磁场和电场联系起来的元件,其固有的、可以与磁场互相作用的能力使其潜在地比其他元件更为敏感。和电容类似,聪明地使用电感也能解决许多EMC问题。下面是两种基本类型的电感:开环和闭环。它们的不同在于内部的磁场环。在开环设计中,磁场通过空气闭合;而闭环设计中,磁场通过磁芯完成磁路。如图4所示.

电感比起电容和电阻而言的一个优点是它没有寄生感抗,因此其表面贴装类型和引线类型没有什么差别。

开环电感的磁场穿过空气,这将引起辐射并带来电磁干扰(EMI)问题。在选择开环电感时,绕轴式比棒式或螺线管式更好,因为这样磁场将被控制在磁芯(即磁体内的局部磁场)。

评论