常见的去耦电容的一些使用方法的详细解析

在科学技术高度发达的今天,各种各样的高科技出现在我们的生活中,为我们的生活带来便利,那么你知道这些高科技可能会含有的去耦电容吗?

本文引用地址:http://www.eepw.com.cn/article/202305/446941.htm前段时间有跟大家分享过去耦电容的有效使用方法——“要点一”使用多个去耦电容,今天为大家继续介绍“要点二”降低电容的 ESL(等效串联电感)

在电路板布线上采取措施,使信号线的杂散电容降到最小;

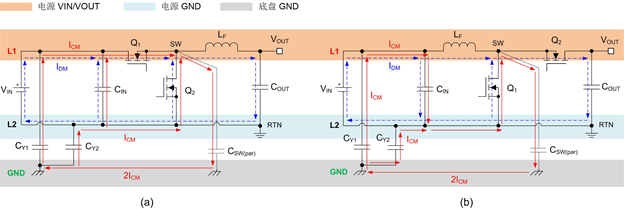

去耦电容的有效使用方法的第二个要点是降低电容的 ESL(即等效串联电感)。虽说是“降低 ESL”,但由于无法改变单个产品的 ESL 本身,因此这里是指“即使容值相同,也要使用 ESL 小的电容”。通过降低 ESL,可改善高频特性,并可更有效地降低高频噪声。

另一种方法是设法降低供电电源的内阻,使尖峰电流不至于引起过大的电源电压波动;

即使容值相同也要使用尺寸较小的电容

对于积层陶瓷电容(MLCC),有时会准备容值相同但尺寸不同的几个封装。ESL 取决于引脚部位的结构。尺寸较小的电容基本上引脚部位也较小,通常 ESL 较小。

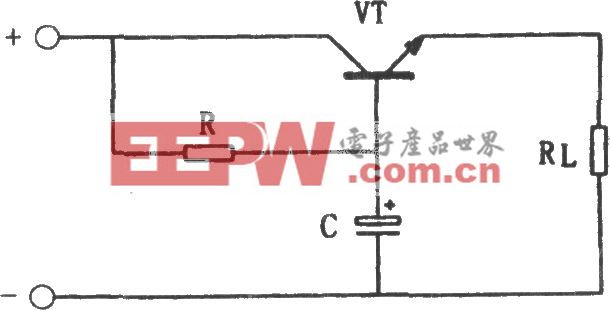

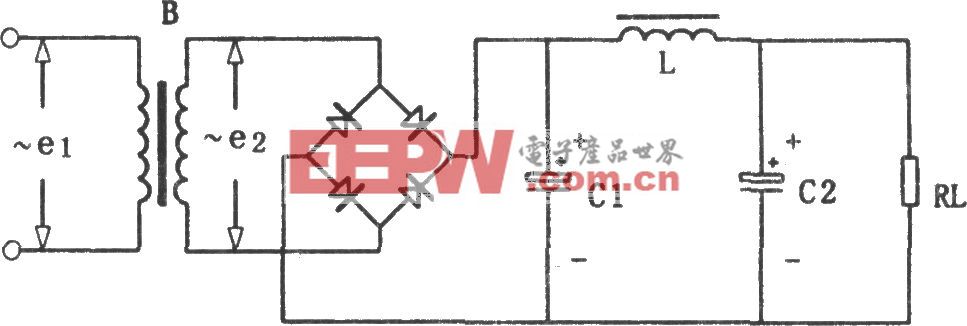

通常的作法是使用去耦电容来滤波,一般是在电路板的电源入口处放一个 1uF~10uF 的去耦电容,滤除低频噪声;在电路板内的每一个有源器件的电源和地之间放置一个 0.01uF~0.1uF 的去耦电容(高频滤波电容),用于滤除高频噪声。

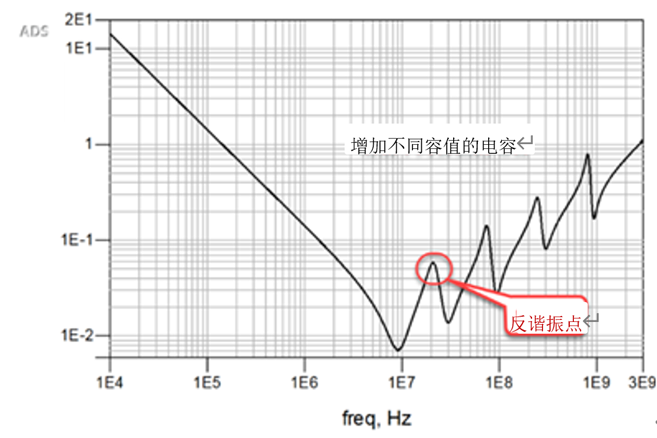

下图是容值相同、大小不同的电容的频率特性示例。如图所示,更小的 1005 尺寸的谐振频率更高,在之后感性区域的频率范围阻抗较低。这正如在“电容的频率特性”中所介绍的,电容的谐振频率是基于以下公式的,从公式中可见,只要容值相同,ESL 越低谐振频率越高。另外,感性区域的阻抗特性取决于 ESL,这一点也曾介绍过。

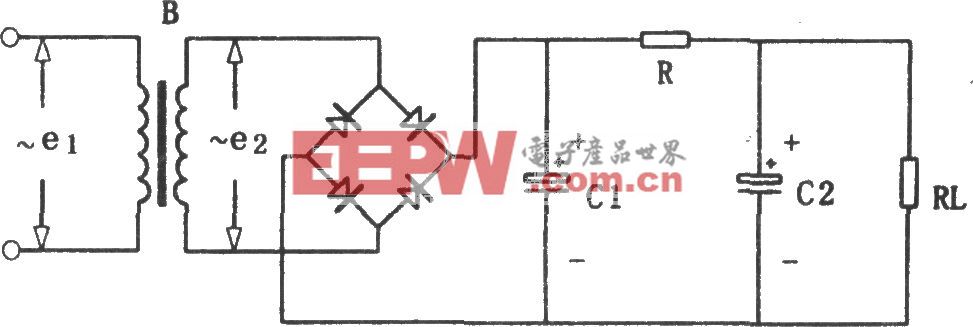

滤波的目的是要滤除叠加在电源上的交流干扰,但并不是使用的电容容量越大越好,因为实际的电容并不是理想电容,不具备理想电容的所有特性。

关于噪声对策,当需要降低更高频段的噪声时,可以选择尺寸小的电容。积层陶瓷电容中,有些型号采用的是旨在降低 ESL 的形状和结构。如上图所示,普通电容的电极在短边侧,而 LW 逆转型的电极则相反,在长边侧。由于 L(长度)和 W(宽度)相反,故称“LW 逆转型”。是通过增加电极的宽度来降低 ESL 的类型。

去耦电容的选取可按 C=1/F 计算,其中 F 为电路频率,即 10MHz 取 0.1uF,100MHz 取 0.01uF。一般取 0.1~0.01uF 均可。

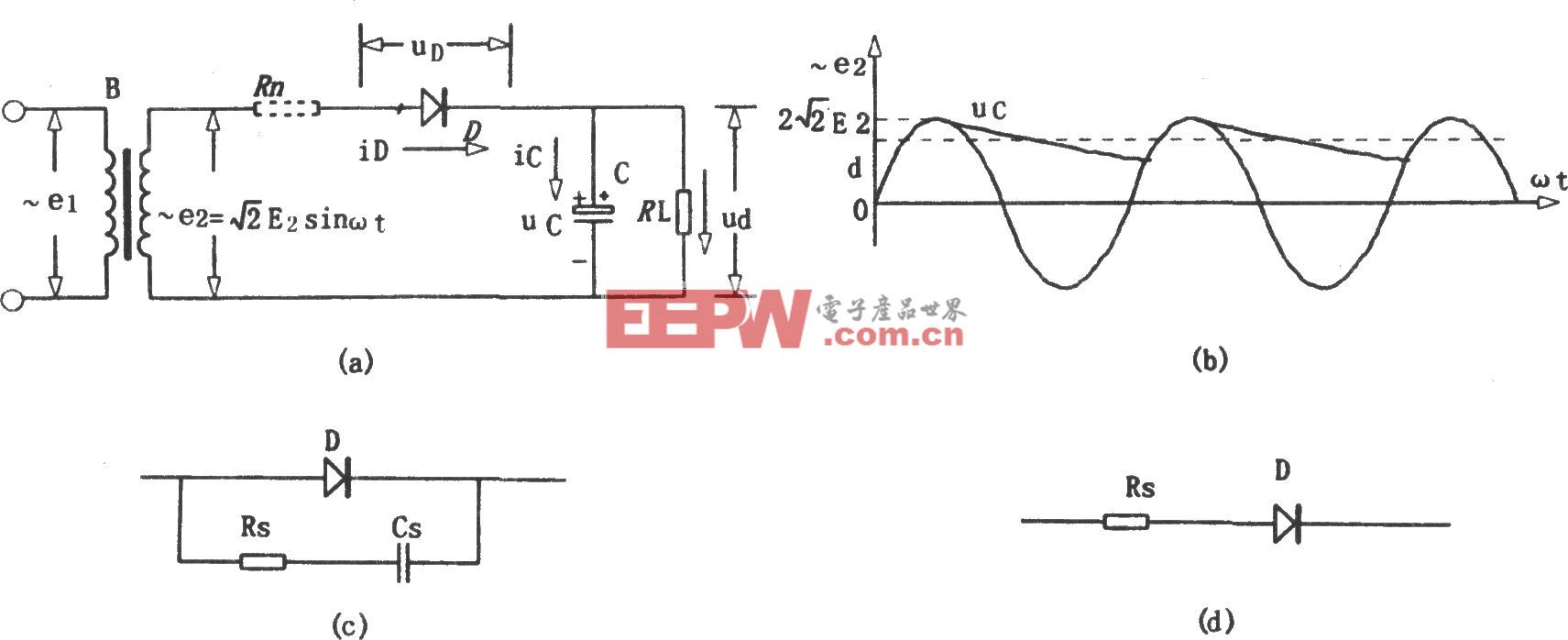

三端电容是为了改善普通电容(两个引脚)的频率特性而优化了结构的电容。三端电容是将双引脚电容的一个引脚(电极)的另一端向外伸出作为直通引脚,将另一个引脚作为 GND 引脚。在上图中,输入输出电极相当于两端伸出的直通引脚,左右的电极当然是导通的。这种输入输出电极(直通引脚)和 GND 电极间存在电介质,起到电容的作用。

放置在有源器件傍的高频滤波电容的作用有两个,其一是滤除沿电源传导过来的高频干扰,其二是及时补充器件高速工作时所需的尖峰电流。所以电容的放置位置是需要考虑的。

将输入输出电极串联插入电源或信号线(将输入输出电极的一端连接输入端,另一端连接输出端),GND 电极接地。这样,由于输入输出电极的 ESL 不包括在接地端,因此接地的阻抗变得非常低。另外,输入输出电极的 ESL 通过在噪声路径直接插入,有利于降低噪声(增加插入损耗)。

评论