用开关稳压器为高速ADC供电

对于挑选高速数据转换器的设计者而言,功耗是最重要的系统设计参数。无论是需要较长电池寿命的便携设计,还是消耗热能较少的小型产品,功耗都很关键。系统设计者过去都采用低噪声的线性稳压器为数据转换器供电,如低压差稳压器,而不是开关稳压器,原因是他们担心开关噪声会进入转换器的输出频谱,从而大大降低AC性能。

不过,较新一代经过噪声优化的开关稳压器(用于手机)可最大限度地减少与相邻低噪声与功率放大器之间的干扰,从而使应用发生了一种转变。它们能够直接从一个DC/DC转换器为高速数据转换器供电,而不会显著降低AC性能。这一设计可立即将功率效率提高20%~25%。

现代高速转换器可较前代减少大约50%的功耗,部分原因是将电源电压从3.3V降低到了1.8V。在一个采用低压差稳压器的设计中,随着电源轨的下降,稳压器的压差以及可用电源轨对功率效率就变得更为重要。电路板的数据部分通常有很多电压轨,为FPGA和处理器提供各种核心与I/O电压。而在模拟部分,可能只有少数“干净”的电压供选择,如3.3V和5V。

对一个高速数据转换器来说,可以用一只线性稳压器,从一个公共5V电压轨获得3.3V电压。这样,低压差稳压器上有1.7V的压降,相当于约35%的功率损失。当采用低压差稳压器(如ADS4149),从3.3V总线上为一只ADC提供1.8V电源时(参考文献1),线性稳压器上的功率损耗增加到大约45%,这意味着低压差稳压器几乎耗散了一半的功率。本例说明低效率的电源设计可轻易损失掉50%的功率。开关稳压器的效率与输入电源轨的大小没什么关系,因此,能节省相当大的功率。通过精心设计,可以将对AC性能的影响降低到最低程度。

电源滤波

隔离来自ADC开关噪声的一个关键元件是电源滤波器,它包括一个铁氧体磁环和旁路电容。在选择铁氧体磁环时应考虑多个关键特性。首先,铁氧体磁环必须有用于数据转换器的充足额定电流,它必须有低的DCR(直流阻抗),以尽量减少磁环自身的压降。例如,当一个200mA电源通过一个DCR为1Ω的磁环时,产生一个200mV的压降。这个压降可能将ADC上的电压推至边沿,考虑到电源电压的标准差,ADC电压甚至可能低于建议的工作电压。

其次,铁氧体磁环必须对开关频率和DC/DC转换器的谐波有高阻抗,以阻挡开关噪声和开关毛刺。市面上大多数铁氧体磁环的阻抗是在100MHz,而现代DC/DC转换器的典型开关频率是500kHz~6MHz。在我们的例子中,ADS4149评估模块采用了一只TPS625290开关稳压器,开关频率为2.25MHz(参考文献2)。由于DC/DC稳压器是方波输出,因此还必须考虑更高阶的谐波。Murata公司的NFM31PC276B0J3EMI滤波器在该频率范围内有高阻抗和低DCR。

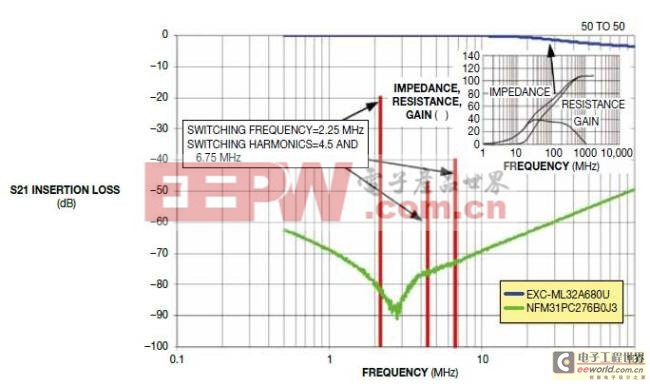

图1比较了一个采用100MHz时电阻为68Ω的Murata EMI滤波器的传统铁氧体磁环插入损耗。电源电路有低的阻抗,在50Ω环境下测出插入损耗。因此,电源滤波器的插入损耗量值可能有少许差异,虽然谐振频率并不变化。

图1,相比一个100 MHz时电阻为68Ω的传统铁氧体磁环,Murata公司的NFM31PC276B0J3 EMI有高的阻抗和低DCR。

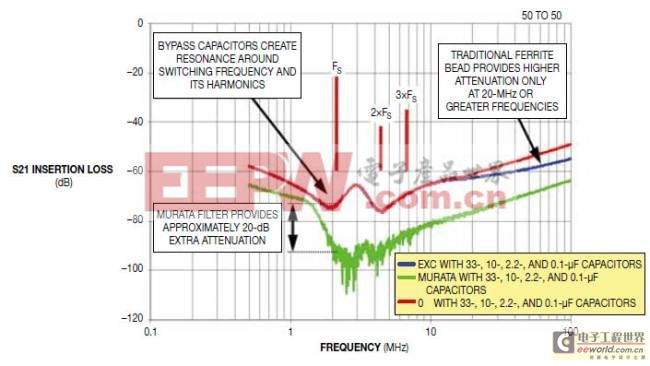

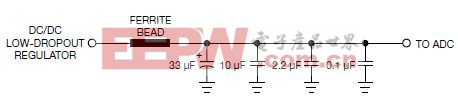

电源滤波器中的其它元件是旁路电容。选择这些电容值时,应使它们的谐振频率(产生一个接地的低阻抗路径)接近于开关频率。这样,通过磁环的开关噪声就被短路到地。图2的电源滤波器插入损耗比较表明,正确的旁路电容值可产生一个接近于开关频率的谐振,即使是用于一只传统铁氧体磁环,如EXCML32A680。不过,在低频时,如果将其与一只0Ω电阻放在一起,就没有那么大差异了。另一方面,Murata EMI滤波器提供了围绕开关频率的大约20dB额外衰减。图3中的电源滤波器使用了一只33μF钽电容做宽频去耦,而10μF、2.2μF和 0.1μF的陶瓷电容则有狭窄的谐振频率。

图2,正确的旁路电容值可产生一个接近于FS(开关频率)的谐振,即使与一个传统铁氧体磁环(如EXC-ML32A680)结合使用。

图3,此电源滤波器采用了一只33μF钽电容做宽频去耦,而10μF、2.2μF和 0.1μF的陶瓷电容则有狭窄的谐振频率。

AC性能

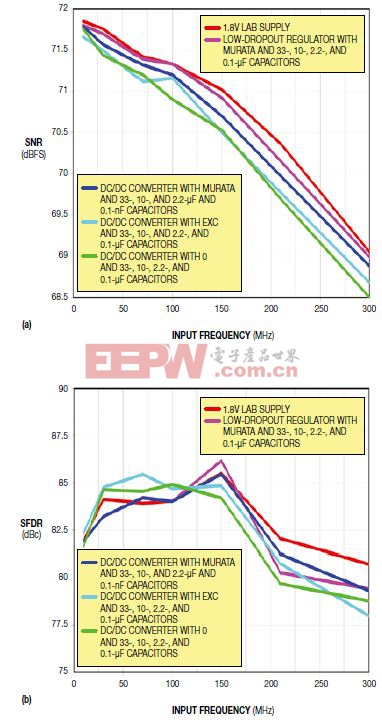

根据数据转换器的PSRR 特性,电源轨上某些噪声量仍能进入ADC,降低AC性能。图4是SNR与SFDR(无杂散动态范围)比较扫频图,其中一个是用低压差稳压器的基准电源(如1.8V的实验室用干净电源),另一个是采用ADS4149评估模块、有不同电源滤波器选项的DC/DC转换器。

图4,这些SNR(a)和SFDR(b)扫频图比较了一个用低压差稳压器的基准电源(如1.8V的实验室用干净电源),以及一个采用ADS4149评估模块、有不同电源滤波器选项的DC/DC转换器。

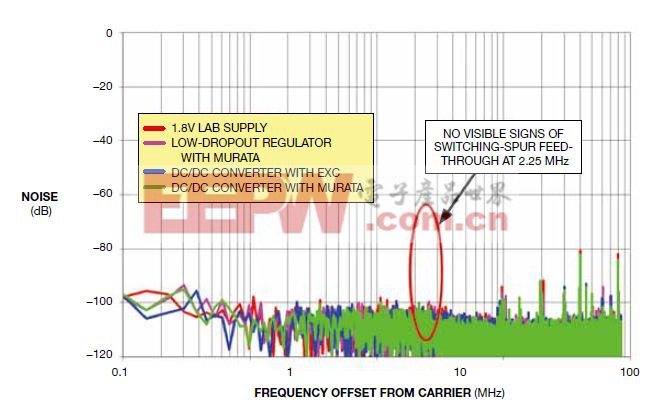

测试结果表明,在300MHz的中间频率下,当用开关稳压器供电时,SNR性能比低噪声低压差稳压器下降了大约0.3dB。而各种方式的SFDR性能几乎相同。通过仔细观察正态化的FFT图(开始于输入信号,绘制的是噪声与偏移频率关系图),表明当使用次优的EXC铁氧体磁环时,整个Nyquist区中的背景噪声略有升高,而没有任何开关频率馈入的迹象(图5)。

图5,正态化的FFT图(开始于输入信号,绘制的是噪声与偏移频率关系图),表明当使用次优的EXC铁氧体磁环时,整个Nyquist区中的背景噪声略有升高,而没有任何开关频率馈入的迹象。

功率效率

用DC / DC 转换器替代线性稳压器的主要优点是节能。在用ADS4149评估模块做的所有实验中,分别采用了外接3.3V电源和一个公共的模拟电源轨,为低压差稳压器和开关稳压器供电。表1给出了测得的功率效率,以及它们相应的静态电流。这种比较表明,低压差稳压器的功耗几乎总是比ADC高得多。开关稳压器功耗较一个理想方案只高32mW,从而获得了一个高效的电源设计。当逐步下调输入电压时(从3.3V起,再到2.5V或2.2V),可以进一步提高低压差稳压器的效率,但要付出更高系统成本和更大体积的代价。

虽然DC/DC转换器设计需要较低压差设计更多的外接元件,但其总体占位面积却可能更小,因为较新型DC/DC转换器有更高的开关频率,从而大大降低了电感的体积,例如,在500kHz下需要33μH,而在2.25MHz下只要约2.2μH。

表1:转换器的比较

反之,线性稳压器可能不需要电源滤波,但它们也有体积限制,因为它们通常要耗散更多功率。从成本角度看,开关稳压器可能成本略高,因为元件数量较多。不过,增加的效率可以抵消散热技术以及系统功率预算的成本(参考文献3与4)。

当系统设计者寻求更高功率效率的元件时,采用将高速数据转换器设计中的电源架构改为开关稳压器的方法,可以节省大量的能耗。你可以用一个开关稳压器直接为一个低功耗的高速数据转换供电,而不会明显降低其AC性能。

评论