一种高速并行FFT处理器的VLSI结构设计

万红星 陈 禾 韩月秋 (北京理工大学 电子工程系信号与信息处理专业,北京 100081)

摘 要:在OFDM系统的实现中,高速FFT处理器是关键。在分析了基4按时域抽取快速傅立叶变换(FFT)算法特点的基础上,研究了一种高性能FFT处理器的硬件结构。此结构能同时从四个并行存储器中读取蝶形运算所需的4个操作数,极大地提高了处理速度。此结构控制单元简单,便于模块化设计。经硬件验证,达到设计要求。在系统时钟为100MHz时,1024点18位复数FFT的计算时间为13µs。

关键词:FFT 蝶形单元 块浮点 流水线

正交频分复用OFDM(Orthogonal Frequency Division Multiplex)是近几年兴起的一种在无线信道上实现高速数据传输的新技术。它采用多载波调制技术,其最大的特点是传输速率高,对码间干扰和信道选择性衰落 具有很强的抵抗能力。在OFDM系统中,各子载波的调制解调采用一个实时的快速傅立叶变换(FFT)处理器实现,因此高速FFT处理器是OFDM系统实现中的一个重要因素。目前通用的FFT模块可以达到的速度数量级为1024点16位字长定点、块浮点、浮点运算在几十到数百微秒量级[1],其中采用TI公司的DSP62XX定点系列达到66μs量级处理速度,新近的64XX在600MHz时钟频率下完成1024点定点FFT的时间仅需10μs。C6701浮点DSP在167MHz时钟频率下完成32位1024点浮点FFT的运算时间需120μs[2]。而AD公司的ADSP-21160 SHARC在100MHz下完成需要90μs。但是如果仅用于FFT处理而废弃其他功能性价比就很低。采用Xilinx公司的FFT IP核处理,也可以达到160MHz的工作频率[3],但由于其采用固核,外围引脚较多不利于使用,且不利于针对特殊要求进行修改。

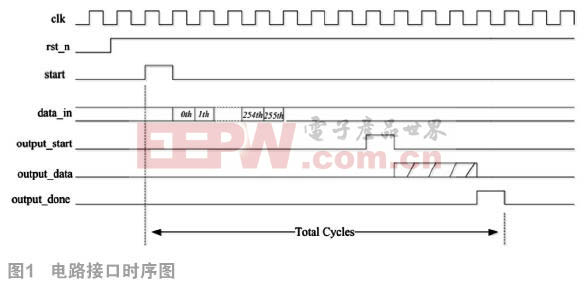

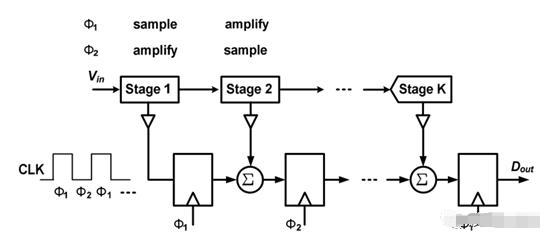

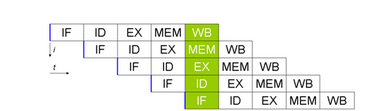

本文在分析了基4按时域分解的FFT算法特点的基础上[4],提出了一种便于VLSI实现的FFT处理器结构。处理器运算单元的流水并行及操作数的并行读写保证了每个周期能够完成一次蝶形运算。而文献[5~6]提出的地址映射算法不适用于本设计单蝶形运算结构;文献[7]中,寻址方案基于线形变换,但是需要复杂的位矩阵点积算法;文献[8]方案做了改进,但仍然较复杂。本文提出一种完全同址的数据全并行FFT处理器设计方法。此方案仅需要一个计数器,通过简单的线形变换,即可实现对不同长度N=4p的FFT处理。

1 原理分析

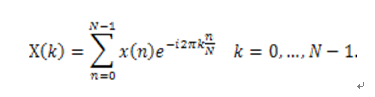

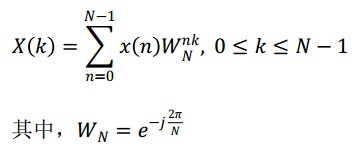

设序列x(n)的长度为N=4p,其中p为正整数,则x(n)的DFT为:

由上述运算步骤可推得基4按时间抽取在第s级的蝶形运算单元的方程为:

其中s为基4 DIT算法流图中蝶形运算单元的级数;n=b2

评论