一种基于功耗管理的DSP处理器设计

摘 要:一种具有功耗管理特性的DSP处理器的结构设计。该处理器采用4级流水线和增强型的哈佛并行系统结构及完善的时钟管理模块,提供了一种DSP处理器的集成设

关键词:DSP处理器 流水线 哈佛结构 低功耗

在信息日益成为一种重要资源的今天,强大的市场需求和微电子技术的发展促成了便携式电子系统的飞速发展。这些便携式电子设备,不但对速度和面积要求非常高,而且对系统的平均功耗要求也很严格,使功耗问题日渐成为制约便携式电子设备发展的瓶颈。要获得高性能低功耗的方案,其实质也就是在处理速度、芯片面积和功耗上来权衡如何满足数字信号处理系统的要求。

本文介绍了一种基于并行流水线的低功耗数字信号处理器(DSP)的系统设计,以改善通用处理器的不足,应用于各种便携式系统中,以便取得良好的效果。

系统方案中,基于流水线的结构从行为级方面降低了系统的功耗;时钟管理方案则可以允许系统在不同的工作模式下使用不同的工作频率,从而使每一个单项任务所消耗的功耗最小;增强型的哈佛结构存储管理可以大大提高系统的并行性,提高系统效率。

1 流水线结构

流水线结构是芯片行为级降低功耗的主要方法之一,下面简要分析其原理。在传统的分析方法中,CMOS电路的功耗可用下面的方程进行估计:

其中f=1/Ts,Ts是原始时序系统的时钟周期。若是一个M级流水线系统,其关键路径则缩短为原路经长度的1/M,一个时钟周期内充放电电容则减小为Ccharge/M(注意总电容并没有变化)。如果时钟速度保持不变,则在原来对电容Ccharge充放电的同样时间内,现在只需要对Ccharge/M进行充放电,这就意味着电源电压可以降低到βVdd,其中β是一个小于1的常数。这样,流水线滤波器的功耗将为:

和原始系统相比流水线系统的功耗降低了β2倍。

该DSP处理器采用如图1所示的4级流水线结构。各级流水线的功能介绍如下:

FI:取址阶段。由程序地址产生模块产生指令存储器地址,并取出指令。

DI:译码阶段。通过指令译码产生相应的微控制信号,送入相应的控制寄存器。

FO:取操作数阶段。从寄存器堆或外部存储器读出相应的数据,通过数据总线送入运算单元或寄存器堆。

EXE/WB:执行及写回阶段。进行运算或操作,得出相应的结果,并将结果放到写总线(EB)上。

图1 4级流水线

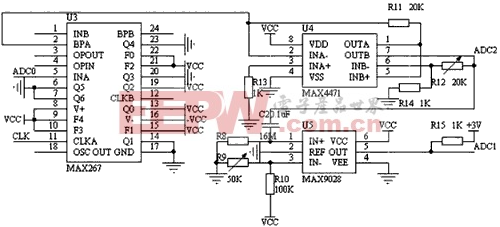

2 外围接口部分

外围接口部分提供系统内部和外部的各种连接方式,实现各种方式的信息传输。本设计把这些接口分为二大部分:(1)MCU类型的接口,如低速的串行端口(串行外围接口(SPI)和通用异步收发器(UART))、可编程通信接口(PCI)、通用串行总线(USB)以及一些外围设备。(2)适于媒体信息收发的高速接口,如异步串行端口和并行外围接口。

3 数据传输的设计

数字信号处理是数据量很大的应用,所以如何高效地传输数据是一个影响系统性能的关键瓶颈。作为DSP处理器,必须有全面的DMA能力以便对数据在芯片内外进行传输。因为在DSP芯片内部集成足够的存储空间不大现实,所以必须采用DMA来管理流动数据,将数据传输和系统控制过程分开。这样,一方面可以提高数据传输的速度,另一方面可以降低处理器内核的负担,提高系统运行效率。

系统设计中DMA采用基于描述符的传送,它在发起DMA传送序列时,需要一组存储在存储器中的参数。这类传送允许将多个DMA序列链接在一起,一个DMA通道可以被编程建立,并且在当前序列完成之后启动另一个DMA传送。

4 乘法器和逻辑单元的设计

在数字信号处理应用中,实现高速的数据运算是其突出的特点,所以其结构设计中必须具有单独的乘法器以实现其性能的提高。乘法器和逻辑单元的结构框图如图2所示。

图2 CALU及乘法器结构框图

乘法器工作时,用1条LT(Load TR)指令加载TR,由TR提供一个乘数。乘法指令提供另一个操作数,它既可以是来自数据总线,也可以是来自程序总线的立即数。不管在哪种情况下,每个周期都可以获得稳定的乘积项输出。

3个移位器(shifter)是桶式移位器,它提供对16位或32位的操作数进行移位操作,可以大大提高乘后累加的速度。

5 地址处理模块

地址处理模块是为总线部件计算取指和取数据的地址,也包括处理一些重复指令和跳转指令。根据指令系统的特点,本文设计的地址处理单元如图3所示。

图3 地址处理模块结构框图

派生地址可能来自S_BUS,或是上一地址的加1值,也可能是总线输入数据暂存器DataIn之一;指令指针IC的值可能来自S_BUS或者是自增1的结果;预取指针PreIC可能来自IC或者是自加1的结果。最后的输出地址是派生地址暂存器AddrTemp、指令指针IC、总线输入数据暂存器DataIn或预取指针PreIC这4种地址之一。

当执行的指令需要计算有效地址时,输出地址是派生地址寄存器;当程序跳转时,输出地址是指令指针IC;当寻址方式是间接寻址时,输出地址是DataIn; 当预取指令时,输出地址是预取指针PreIC。

因为AddrTemp和IC的增量计算在系统中不可能同时出现,所以结构设计中只设计一个增量器供二者共用。

6 存储器的组织管理

在数字信号处理系统中,数据的吞吐率直接影响系统的性能,传统的冯

评论