WIMAX LDPC码译码器的FPGA实现

摘 要: 设计了基于TDMP-NMS算法的码率码长可配置LDPC码译码器,支持WIMAX标准LDPC码的译码。 通过插入最短的额外时钟周期,使得更新后的节点信息得到了及时利用。采用一种工作于增量模式的基于填充算法的桶形移位寄存器结构,实现了对该标准中576、768、1152、2304 4种码长LDPC 码译码的支持。结果表明所设计的译码器完全能满足WIMAX标准对数据吞吐率的要求。

关键词: WIMAX;低密度奇偶校验码译码器;FPGA;TDMP;归一化最小和算法

全球微波互联接入WIMAX是一种基于IEEE802.16e标准的无线城域网WMAN技术。该技术采用LDPC码作为其信道编码方案。WIMAX标准的LDPC码由于其优异的性能而引起了人们的广泛关注。Torben Brack等人根据该标准中各个码率LDPC码校验矩阵的不同特点,对码率为1/2和2/3B的LDPC码采用TDMP译码算法,对其他4种码率的LDPC码采用BP算法。设计实现了一个可支持WIMAX标准中所有码率和码长的LDPC码译码器[1]。SHIH Xin Yu等人对LDPC码的校验基矩阵进行行列置换,使得变量节点和校验节点的处理在时间上可以部分重叠,基于BP算法实现了支持该标准中码率为1/2 的19种码长的LDPC码的译码器[2]。

重组网络是部分并行LDPC码译码器中的一个重要组成单元。对数移位寄存器结构和双向网络仅适用于单个码长。为了实现对多种码长的支持[3],采用了Benes网络,基于该网络的部分并行译码器可支持扩展因子小于该网络输入输出端口数的各种码长LDPC码的译码。由于该网络中各个开关控制信号的产生是基于一种递推的算法,因此其复杂度较高。

本文将TDMP算法运用于WIMAX标准中所有6种码率的LDPC码的译码,通过分析得出了各个码率LDPC码的变量节点后验LLR在前后两次更新之间的最小时间间隔,采用插入额外时钟周期的方法使得更新后的节点信息得到了及时利用。设计了一种基于填充算法的桶形移位寄存器结构的重组网络单元,实现了对该标准中576、768、1152和2304 4种码长的支持。采用了基于增量的循环移位模式,降低了硬件实现复杂度和单次迭代处理的周期数,提高了吞吐率。

1 LDPC码的译码算法

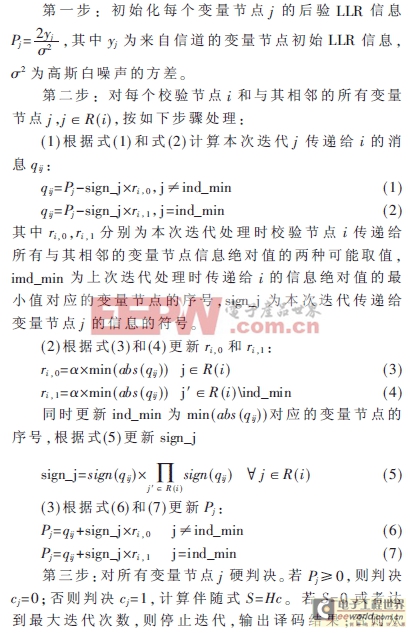

LDPC码的标准译码算法为BP算法。TDMP及时利用了更新后的节点信息,加快了译码收敛速率。中高信噪比条件下,该算法成功译码所需的平均迭代次数仅是BP算法的一半。TDMP-NMS算法采用归一化最小和算法更新TDMP算法中的校验节点信息,简化了运算复杂度。该算法的译码处理步骤如下[3]:

(2)开始继续下一次迭代处理。

评论