基于SEP3203为核心的工控系统

引 言

S680724显示控制芯片将控制电路、RAM和驱动电路集成在单一芯片中,使其在系统成本方面具有优势。SEP32O3是由东南大学国家ASIC工程中心设计的一款基于ARM7TDMI内核的16/32位嵌入式微处理器。虽然SEP3203自带LCD控制器,但是其信号适用于不带RAM的灰度或彩色液晶屏,不支持在工控系统中常使用的带RAM的黑白液晶显示屏,所以工控系统应用中需要通过外接显示控制器来实现液晶显示。下面介绍S680724显示控制器在以SEP3203为核心的工控系统中的应用。

1 系统介绍

1.1设计要求

系统要求通过总线挂接的方式实现64×192黑白点阵的显示。该点阵屏的规格较特殊,但在电话终端和小型收款机等工控系统中经常使用。常见的几款中小规模显示由DSP自身的硬件来协调冲突,因此HPI-8口适用于与单片机构建较好的主从双CPU处理器平台。控制器[2.3]所控制的点阵范围都比其小(65×132,132×176)。

需要用2片S680724控制该液晶屏,同时要求只使用1个片选信号来实现对2片S680724的控制。

1.2系统构成

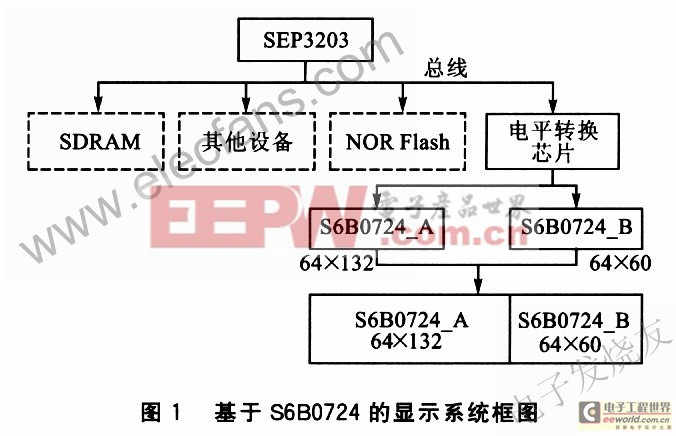

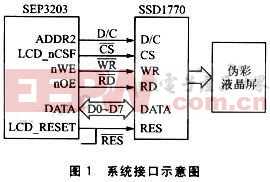

系统主要由SEP3203处理器、电平转换芯片74LVXC4245和74HCT541,以及2片S680724显示控制器组成,如图1所示。SEP3203是一款16/32位嵌入式微处理器,由东南大学国家ASIC工程中心设计。采用业界标准的ARM7TDMI内核,AMBA总线结构。SEP3203处理器内嵌20 KB零等待的静态存储器(SRAM),提供SDRAM控制器;可支持NOR Flash、NAND Flash启动;可扩展支持各种SRAM接口的设备;提供可自由控制的GPIO口,同时具有多种控制器接口。

S680724是一款显示控制驱动芯片,最大支持65×132的点阵显示,同时提供主从式结构的扩展;内部带有RAM,可以支持屏幕自刷新;有65个common输出,165个segment输出。它的MPU接口可支持8080和6800两种时序模式。模式的选择通过配置外部引脚来实现。

由于单片S680724只支持65×132点阵的显示,而设计要求实现64×192点阵的显示,因此在图1中使用了2片S680724。另外,由于S680724使用5 V信号,Vm的最小值为4 V(0.8VDD),而SEP3203的总线采用的是3 V信号(通常的嵌入式CPU使用的都是3 V总线),所以SEP3203无法直接驱动S680724,需要作电平转换。因此图1中在SEP3203与S680724之间增加了电平转换芯片,以实现3 V信号与5 V信号的双向转换。

电平转换芯片选用的是74LVXC4245 和74HCT541。这两款芯片都是普通的逻辑芯片,很多公司都生产。74LVXC4245是双向电平转换芯片,3 V和5 V两路电源供电;可以支持3 V到5 V的双向电平转换,但需要有信号控制电平转换方向。74HCT541是单向的缓冲芯片,采用5 V电源,可以将输入的3 V信号转换成5 V信号后输出。

2 硬件设计

2.1 总线接口的分析

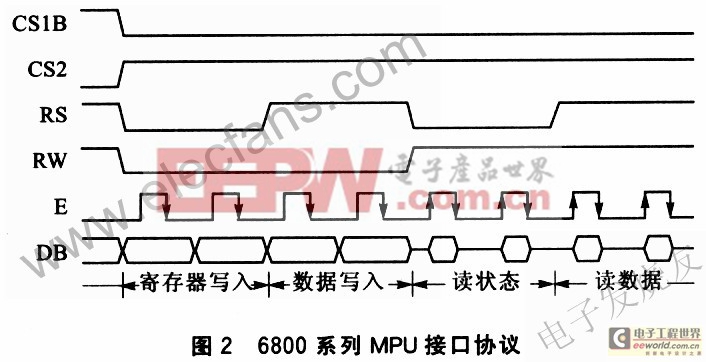

S680724可与各种MPU相连,具体连接方式取决于MPU所使用的总线类型。其提供两种MPU的信号接口协议:一种是6800系列MPU接口协议,如图2所示;另一种是8080系列MPU接口协议.如图3所示。将两种接口协议与SEP3203的接口协议对比,可见SEP3203的接口协议属于8080接口协议,因此采用8080的接口实现S680724与SEP3203的连接。SEP3203的接口协议如图4所示。

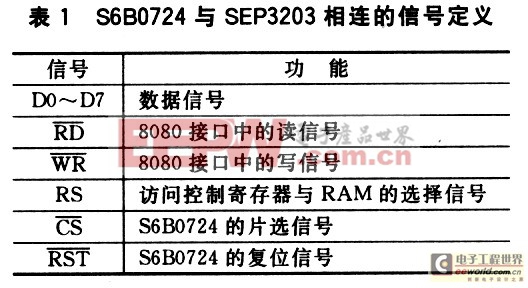

根据8080接口协议,S680724与MPU接口信号的定义如表1所列。

S680724的DO~D7信号应与SEP3203的DATAO~DATA7信号连接;S680724的RD、WR、CS信号应分别与SEP3203的OE、WE、CS信号连接。RS是访问控制寄存器与RAM的选择信号——RS为低时访问S680724的控制寄存器.RS为高时访问S680724中的RAM。其作用相当于地址信号,因此与SEP3203的地址线连接。RST是S680724的复位信号,可由SEP3203的GPIO产生。

2.2双8680724控制器接口设计

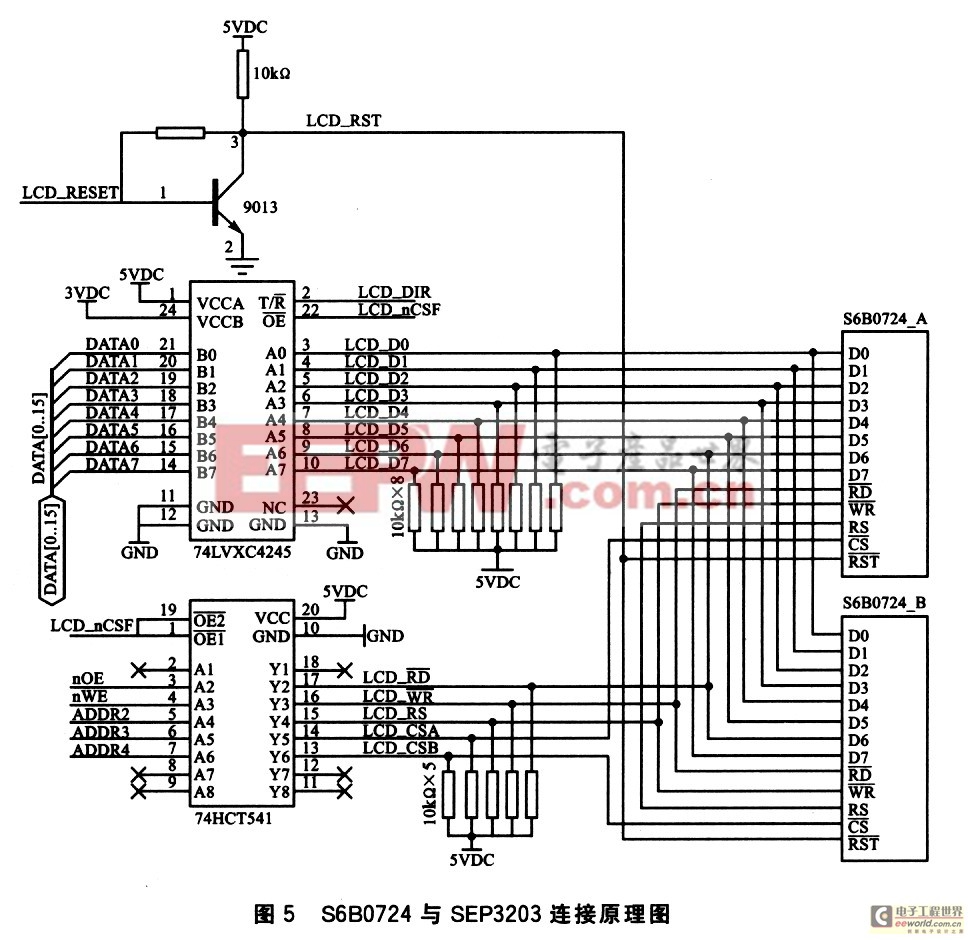

由于要支持64×192的点阵显示,所以在该设计中需要使用2片S680724(以S680724一A和S680724_B来表示)。图1中S680724_A控制液晶屏的64×132个点,S680724_B控制剩下的64X 60个点。由于总线设备较多,只有1个片选信号能用于对2片S680724芯片的操作;同时56130724与SEP3203的总线也需要作电平转换,因此在该接口设计中利用了电平转换芯片实现了该功能,并没有再增加额外的逻辑芯片。分析S680724与MPU的接口信号,发现其中RD、WR、RST、CS、RS信号只需单向传输(从MFU传向S680724),只有DO~D7信号需要双向传输。图5中,使用74HCT541实现3 V信号到5 V信号的单向电平转换,74LVXC4245实现3 V信号与5 V信号的双向电平转换。

图3中CSlB、CS2、RS信号是同时变化的(CSlB信号为低,CS2信号为高时S680724被选中)。由于在实际使用中

CS2信号是固定接高电平,所以CSlB信号就是文中S680724芯片的CS信号。图4中SEP3203总线的地址信号和片选信号也是同时变化的,因此考虑使用地址信号来代替片选信号。但如果直接用地址信号来代替片选信号会导致总线对其他设备操作时也选中S680724,即两个总线设备被同时选中,从而产生错误。在该设计中,利用电平转换芯片的特性解决了这一问题。如图5所示,使用了ADDR3、ADDR4作为S680724的片选信号(LCD_CSA、LCD_CSB)。ADDR2作为选择对S680724寄存器或RAM操作的信号(LCD)_RS)。SEP3203的片选信号ICDnCSF连接74HCT541的使能端()E。当LCD_nCSF信号为低时74HCT54l被使能,OE、WE、ADDR3、ADDR4、ADDR2信号被转换成相应的5V信号(LCD/RD、LCD_/WR、LCD_CSA、LCD_CSB、LCD_RS)输出到S680724;当LCD_nCSF信号为高时74HCT541停止工作,此时74HCT54l输出高阻态,为避免噪声干扰,输出端信号LCD_/RD、LCD_/WR、LCD_CSA、LCD_CSB、LCD_RS应被上拉至5 V。在SEP3203的片选LCD_nCSF无效(高电平)时,由于信号LCD_CSA、LCD_CSB被拉高,所以此时2片S680724控制器都未被选中,任何操作对其都是无效的,从而避免了在总线对其他设备操作时可能对S680724产生的误操作。

数据信号的电平转换类似于控制信号的电平转换。74LVXC4245是双向电平转换芯片,图5中的LCD_DIR信号由SEP3203的GPIO产生,用于控制74LVXC4245电平转换方向的信号。当LCD_DIR为低时,信号由B端传向A端,即由总线传向S680724(写操作);当LCD_DIR为高时,信号由A端传向B端,即由S680724传向总线(读操作)。信号LCD_DO~LCD_D7也需要上拉,防止当74LVXC4245的输出为高阻时,外部噪声在其输出端产生错误信号。

值得一提的是,S680724显示控制器在PCB板上的位置靠近液晶屏,与SEP3203之间的距离很大。在PCB布局时,需要注意电平转换芯片的位置。因为其不但有电平转换的作用,而且还能缓冲总线信号,使总线和S680724显示控制器隔离,避免总线过长。电平转换芯片的布置应该尽量靠近总线,减小总线的长度,从而避免产生由总线过长造成的信号延时及噪声干扰问题。

虽然RST信号也是单向传输的,但RST信号的电平转换电路却是单独设计的。如果使用74HCT541完成电平转换,会有两个问题:①当LCD_nCSF失效时74HCT541不工作,此时LCD__RESET信号无法传递到RST端,RST端始终是高电平(被上拉至5 V),因此S689724无法被复位;②在74HCT541工作时,因为LCD_nCSF的脉冲宽度等于总线周期(最大值约为几百ms).所以输出的RST信号的最大脉冲宽度也等于总线周期;而S680724要求的RST信号最小脉冲宽度是1μs,所以用74HCT541无法产生正确的RST信号,此时S68072同样无法被复位。在图5中,该信号的电平转换电路是由晶体管和电阻构成的。

3 驱动程序

该部分软件主要是依照S680724的初始化流程、命令参数列表及其他资料编写的。S680724的访问 地址只有两个:一个是寄存器地址(通过写入不同的命令字来实现对S680724的控制);另一个是RAM端口(显示数据由此写入)。

首先需要根据S6B0724的接口设计计算其各端口的访问地址。SEP3203的片选信号LCD_nCSF所对应的基址是0x34000000。图5中S680724_A、S680724_B的寄存器访问地址分别是0x340000100、0x34000020;RAM的访问地址分别是0x34000018、0x34000028。特别是在该接口设计允许SEP3203同时访问S680724_A和S680724_B,寄存器的访问地址为0x34000000,RAM的访问地址为0x34000008。在实际使用中。可以利用这个特点对两个控制同时初始化,提高软件效率。

S680724的初始化流程如图6所示。先冷复位S680724,然后将74LVXC4245的电平转换方向设置为从总线向数据线。通过写S680724的控制寄存器对S680724软复位,然后选择所用的显示方式和扫描方向,再选择背光亮度;通过写寄

存器的方式打开S680724内部的电压反转器,等待10 ms后再打开电压生成器。延迟10 ms后,打开电压跟随器,等所有电压都稳定后(约等待10 ms)再设定液晶屏的工作电压,最后开始显示。图像的显示通过函数void Write_alILCD(void)来实现。其功能是将所要显示的点阵数据送入2片S680724。

初始化程序如下:

void GPC)_init(void){

RESET_LCD();

//冷复位

*(RP)PORTB_SEL l=(18);

//设定74LVXC4245的电平转换方向

*(RP)PORTB_DATA 8L=~(18);

*(RP)PORTB_DIR=~(18);

*(RPl6)ADDR_LCD_CMD=INTER_RESET;

//2片S6B0724B同时软复位

1NIT_LCD(); //初始化S680724B

*(RPl6)ADDR_LCD_CMD=DISPLAY_ON;

//初始化完毕开始显示

Clear_LCD(); //清屏

}

4结论

该设计已在以SEP3203为核心的嵌入式系统中被实际应用。采用S680724显示控制器后,解决了SEP3203微处理器在工控应用中使用液晶屏的问题。使用1个片选信号实现了对2个显示控制器的控制。2个以上显示控制器的控制也可通过类似方法实现。该设计可以在金融收费系统、税务管理系统、电话终端等众多系统中应用。

评论