基于AVR单片机的USB 0TG主从机系统设计

随着PDA、移动电话、数码相机、打印机等消费类产品的普及,用于这些设备与电脑、或设备与设备之间的高速数据传输技术越来越受到人们的关注。以往以计算机为核心的数据传输结构,非常不利于USB,总线在嵌入式行业的应用,也不适用于野外作业,而OTG技术的推出则可实现在没有PC的情况下,设备与设备之间的数据传输,它拓展了USB技术的应用范围。本文采用的设计方案是基于Philips公司的ISP1362 OTG控制芯片,参照最新的USB OTG技术规范,设计了一种遵循USB协议的主/从机系统。

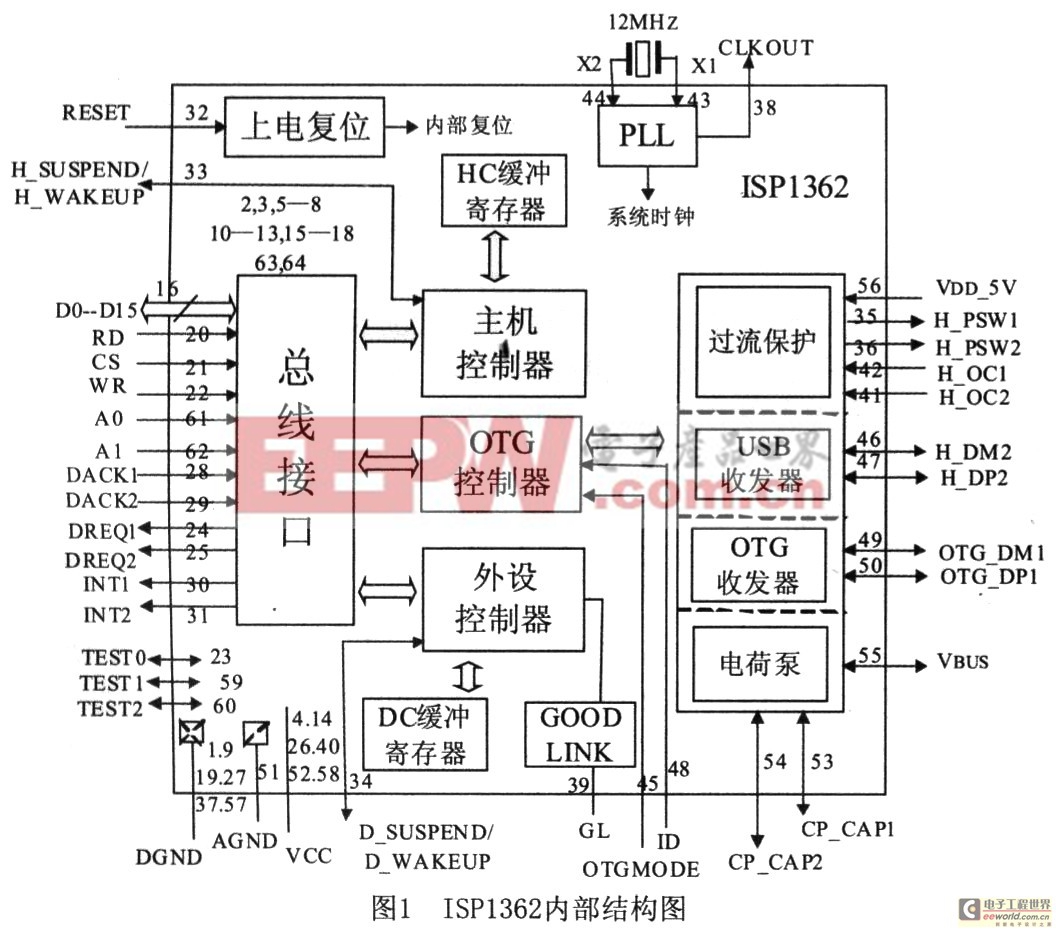

1 ISP1362芯片的内部结构

Philips公司的ISP1362是一款符合USB 2.0总线协议的接口芯片,内部有3个USB控制器一主机控制器、设备控制器和OTG控制器。其中,主机控制器具备高度优化的USB主机功能;设备控制器则具有多达14个可编程端点,又可以被配置成双缓冲端点进一步提高吞吐量:而OTG控制器主要提供包括监控和转换功能在内的所有OTG控制。ISP1362内部构造如图1所示。

2 USB OTG主/从机系统设计

USB OTG主/从机系统设计包括硬件设计和软件设计两大模块。其中硬件电路主要是USB接口电路板的设计;软件设计包括设备初始化、系统的功能设计、设备驱动程序设计等,下面分别介绍系统软、硬件系统的设计方法。

2.1 系统硬件电路设计

USB OTG主/从机设计的硬件电路如图2所示,图中ATmega 32的PD口和IPA口用于控制ISP1362的时序,PB口和PC口则用于与ISP1362的D[0..15]进行数据交换。ISP1362芯片有Port1和IPort2两个USB接口。Port1是个综合接口,可以配置成downstream、upstream或者是OTG;Port2是作为固定的downstream,主要接一般的USB设备。当ISP1362做主机时,主机内部的寄存器通过检测其相应状态寄存器的值就可以判断是Port1还是Port2接了设备,从而进行相应的处理。

评论