基于AVR单片机的USB 0TG主从机系统设计

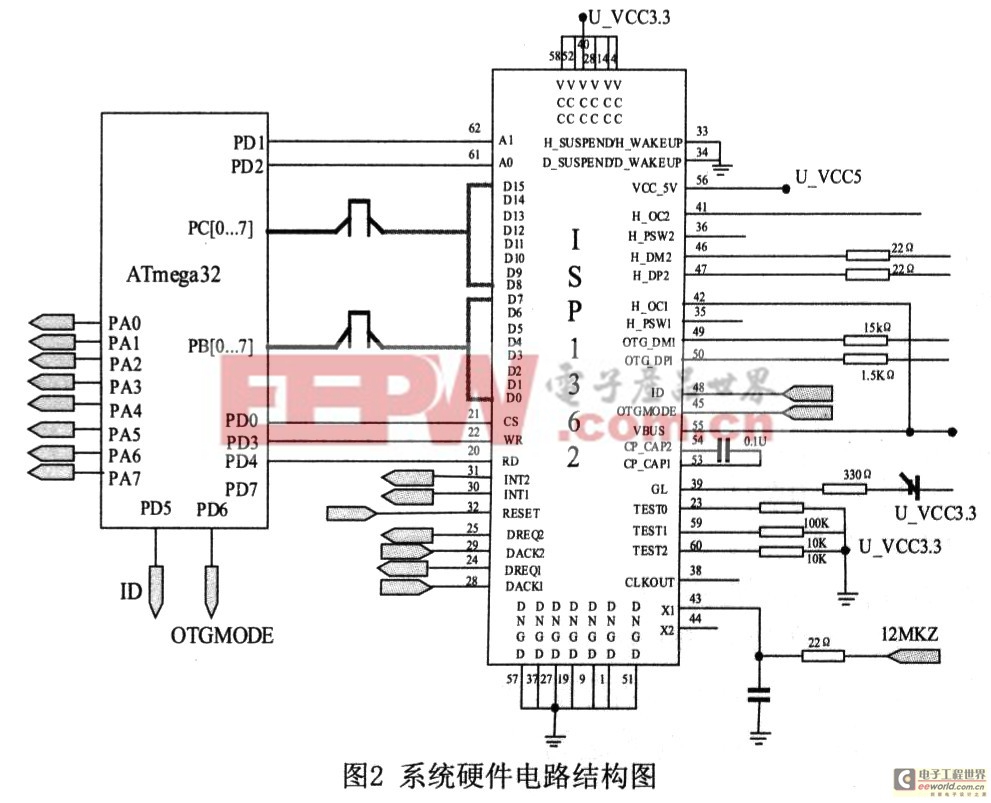

ISP1362的Port1口主/从机功能通过ID、OTGMODE两引脚电平的高低组合来确定。当OTGMODE引脚接低,无论ID电平如何,则芯片的Port1口只能OTG用;如果OTGMODE接高,ID接低,芯片的Port1口作主机使用;OTGMODE接高,ID也接高时,则芯片的Port1口作外设使用。在电路中通过15kΩ的上拉电阻和下拉电阻实现ID、OTGMODE两引脚电平的高低变化。

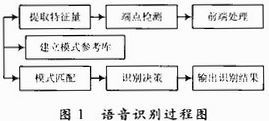

2.2 系统软件设计

本设计的主机系统是一个软件和硬件的集合体,功能的实现不依赖于任何操作系统,而是通过中断来调度各个任务,使之满足USB通信的要求,因此系统是按照协议规范和特定的时序运行的。

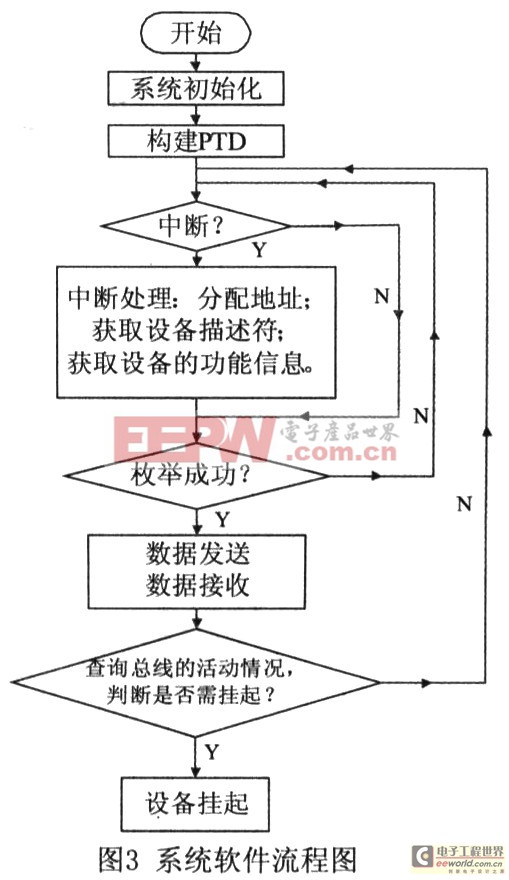

本系统是ISP1362工作于主/从机模式下的应用,按系统硬件电路配置完成接口芯片,然后对其编程,就可以进行USB数据传输。系统工作流程如下:首先进行系统初始化,构建PTD传输描述符,接着总线枚举过程,给外设分配地址,获取外设的基本信息,并判断外设为主机设备或是从机设备,之后驱动相应的主/从机驱动程序运行,数据传送和接收,根据总线的活动情况判断是否挂起。系统流程图如图3所示:

实现ISP1362芯片的软件编程控制,就是对该芯片的CS、RD、WR、A0、A1引脚的控制。本文中CS代表片选,低电平有效;RD代表读信号,低电平有效;WR代表写信号,低电平有效;A0引脚电平的高低不同,分别表示传输的信号代表的是命令信号还是数据信号;A1引脚电平的高低不同,分别表示控制的是外设还是主机。通过上述几个引脚信号的组合,可以实现读写控制ISP1362的不同功能。除此之外,以下的几个引脚对于控制ISP1362也有重大意义:DREQ1引脚代表DMA请求输出,当它高电平有效时,通知IDMA控制器主机正在请求数据传送;DREQ2引脚高电平有效时,通知DMA控制器外设正在请求数据传送;DACK1引脚代表DMA确认输入,低电平有效时表明来自主机的DMA传输请求已经被DMA控制器确认;DACK2引脚低电平有效时表明来自外设的DMA传输请求已经被DMA控制器确认;INT1和INT2引脚连接到外部微处理器的IRQ引脚,使得ISP1362可以根据请求执行中断服务程序。软件设计具体工作流程如下:

评论