以高速缓存和片上闪存实现微控制器近似的确定性

为了控制执行机构,实时控制系统要从传感器接收输入信号,经控制运算后向执行机构输出指令信号。这些输出必须在接收到输入后的规定时间内被触发——即系统需具有实时性;同时,对相同控制状态下的相同输入,输出也应当始终相同——即系统需具有确定性。

电子行业中众多领域的发展正在使这些基本的实时控制系统变得越来越复杂。一方面,控制算法越来越精细,达到了人工智能的决策水平。另一方面,这些控制系统越来越多地连网,即与以太网或无线局域网 (LAN) 进行局域连接,以及与互连网连接实现远距离通信。此外,用户界面也变得越来越复杂,对安全性的要求也越来越高,使得数据加密和外部控制源的合法性验证成为系统不可缺少的功能。

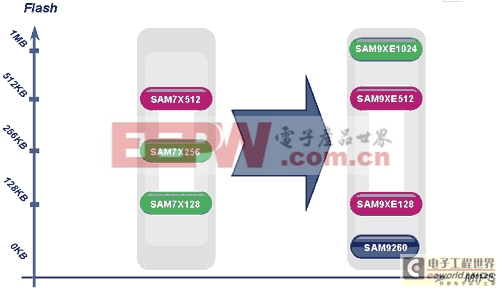

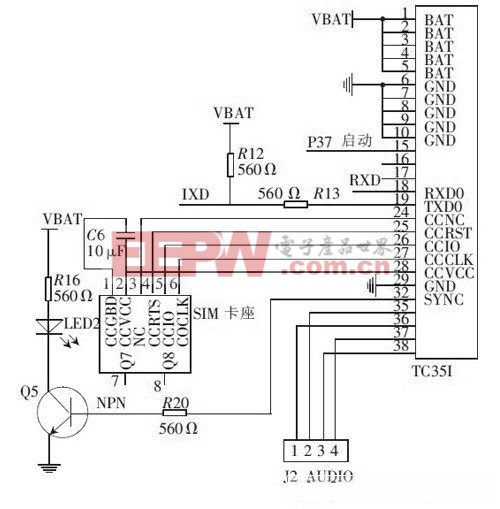

这些发展趋势使得处理器必须具备更强大的处理能力和更高的通信带宽。处理器必须能够按照某种确定的方式对实时输入信号做出响应,同时还必须有足够的存储能力来处理各种网络通信 (作为低优先级的任务)。然而,在很多情况下,为提高性能而进行的系统升级需要保留原先的设备驱动程序、网络协议堆栈以及作为控制算法基础的一些基本运算操作。采用工业标准的处理器构架尤其如此,如32位ARM RISC。图1给出了一个遵从这两个原则的MCU升级的实例,即将以ARM7为基础的AT91SAM7X系列升级为以ARM9为基础的 AT91SAM9XE 系列。这两个系列的器件均有用于存储程序代码和参考数据的片上闪存。

这两个系列的一个重要差别在于:ARM9处理器具有指令和数据高速缓存,而ARM7处理器没有。高速缓存有助于缓解由于处理器和内存之间的能力差异(前者能以约200MIPS的速度运行代码,而后者只能以约25MHz的速度传输数据)而造成的性能下降。众所周知,在采用缓存的系统中不可能实现完全的确定性。不过,ARM926EJ-S处理器和AT91SAM9XE微控制器系列的很多架构特性可让应用开发人员实现近似确定的实时性能。

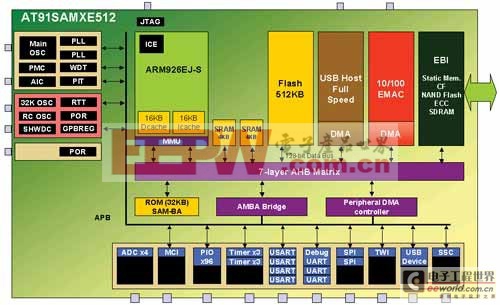

很多架构上的特性可最大限度地提高内部数据传输带宽。如图2所示,以AT91SAM9XE系列为例,除具有单独的、且能以处理器速度工作的16Kb 指令和数据高速缓存外,还通过一个7层AHB总线矩阵在处理器、外设和内存之间建立并行数据通道。USB主机和以太网MAC外设都有专门的DMA端口来实现自主数据传输,而其APB外设则配有外设DMA控制器(PDC),使内存和网络接口间的批量数据传送几乎不占用处理器资源。高级中断控制器(AIC)可在规定的处理器周期数以内处理一系列优先的中断向量。

图1 AT91SAM7X系列升级为AT91SAM9XE系列

图2 AT91SAM9XE架构

高速缓存使处理器能按其所要求的速度及时获得指令和数据,除非缓存当中未缓冲所需的数据或指令。遇到这种情况,处理器就得闲置一会儿,直到高速缓存被重新填充。高度并行的DMA数据传输机制能减少处理器对数据传输的介入,但并非完全不介入。因为任何时候都有可能出现中断请求,即使只需很少的周期来处理该中断。那么如何才能保证系统在规定的时间内,根据给定的输入触发确定的输出呢?

如何获得确定性

要获得确定性,可将存储在闪存中各个关键性操作的代码分解成小于16Kb的模块。将所需的模块加载到指令缓存中,并锁定,以确保执行该模块期间它始终在高速缓存中。如有必要,相关的数据结构也可加载和锁存在数据缓存中。这里,锁存功能是通过高速缓存的锁存寄存器来实现的。这样就可保证关键代码按处理器的速度执行。

如果某一高速缓存正好没有所需的指令代码,则该缓存将通过它与片上闪存间的128位数据总线重新加载所需的指令代码。该总线能以4倍于处理器时钟的速度加载32位数据,大大缩短了刷新高速缓存的时间。此外,缓存的回绕功能 (wrapping) 可确保遗漏的关键数据被优先加载。

考虑到所有这些因素,计算出执行时间,并对同时出现多个中断和DMA传输作最坏打算,就能确定是否能满足实时性约束,以及还有多大的余量。必要时,也可针对每种可能情况编写一些后退程序,允许系统在无法达到实时要求时,以故障弱化方式 (fail-soft,即工作可靠但性能下降的方式) 运行。

结论

仔细设计应用代码,充分利用处理器内核的关键架构功能,将能在基于复杂控制算法的嵌入式连网实时控制系统中实现近似的确定性。这些关键架构功能包括:数据和指令高速缓存的锁存、回绕功能、连接高速缓存和片上闪存的128位宽度的数据总线、低迟滞高级中断控制器,以及用于在外设、网络接口及片上/片外闪存间直接传输数据的DMA控制器。

评论