新型网络数字摄像系统的设计

|

|

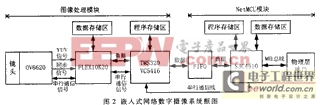

1 图像处理模块

1.1 芯片介绍 图像采集芯片采用OmniVision公司的CMOS彩色图像传感器OV6620[1]。在它内部集成了一个356×292的彩色图像阵列。该图像传感器能对所拍摄的图像进行预处理,包括自动曝光控制、自动白平衡调节、gamma校正、自动图像增强;并可通过与DSP芯片相连的串行通信接口,对传感器内部的92个寄存器的参数进行设置。

图像压缩芯片采用TI公司的TMS320VC5416[2]定点运算数字信号处理器(DSP),其内部采用一种改进型的哈佛总线结构(一条程序总线,三条数据总线),数据总线宽度为16

bit。分开的数据和指令空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上其高度优化的指令集,使得该芯片具有很高的运算速度,最高可达

160MIPS。

VC5416芯片的外部程序存储空间为8M×16bits,外部数据存储空间为64K×16bits。在芯片内部还集成了128K×16bits片上存储器。该芯片具有多种片上外部设备单元,包括一个16位计时器,一个6通道DMA传输控制器,三个带缓冲器的串行通信接口(McBSP

)和一个8/16位的主机通信接口(HPI8/16)。

1.2 功能介绍

图像处理模块主要负责模拟图像的采集、数字化、压缩等工作。首先,在系统加电运行后,由NetMCU模块对VC5416芯片复位,然后VC5416芯片运行固化在芯片内的BootLoader程序,将存储在外部程序存储器上的应用程序复制到内部存储器中,并开始运行应用程序。应用程序的任务主要有以下三个方面:

(1)通过VC5416芯片的1号串行通信接口(McBSP1)对OV6620的内部寄存器进行参数配置。主要参数包括:将输出图像分辨率设置为352×288,将输出图像帧的速率设置为25帧/秒,将数字图像的输出格式设置为YUV分量4:2:2格式。

(2)将OV6620芯片输出的图像数据利用JPEG算法进行数字图像压缩。在本设计中采用一种改进的JPEG算法[4]。将二维DCT变换分解成两次一维快速DCT变换。对8×8象素块的DCT变换,共需176次乘法和464次加法,比标准DCT算法的1024次乘法和896次加法在运算速度上有极大提高。

(3)VC5416芯片通过与NetMCU模块相连的0号串行通信接口(Mc BAP0),接收改变传输图像的分辨率、帧速、曝光时间等参数的命令,并及时调整OV6620芯片的内部寄存器参数。

OV6620芯片和VC5416芯片之间存在大量的数据传输,因此在系统中采用一片ALTERA公司的FPGA(FLEX10K20)芯片作为数据传输接口,代替VC5416芯片管理外部数据存储区。在FPGA芯片中集成了一个512×16bits的FIFO和一个存储控制器。通过OV6620芯片输出的图像象素移位脉冲和图像的行、场同步脉冲的控制,将原始图像数据存入FIFO中。由于JPEG图像压缩以8×8象素块基本运算单位,需要存储控制器将FIFO中以行顺序输入的原始图像数据进行存储地址调整,变换成按8×8像素块顺序存入外部数据存储区。同时,由于受VC5416芯片的外部数据存储区容量的限制,存储控制器将一帧原始图像数据分成上下两个半区,各占用一个64KB地址空间。当VC5416芯片读数据时,存储控制器会自动在这两个半区之间切换,使得DSP芯片能够处理一帧图像。

2 NetMCU模块

2.1 芯片介绍

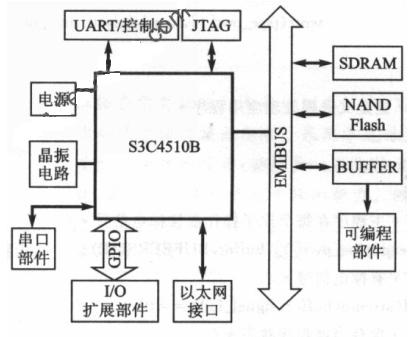

本系统采用三星公司的S3C4510B[3]芯片作为主控制器。芯片内部结构见图3。S3C4510B芯片集成了ARM公司的32位精简指令集处理器ARM7TDMI核。ARM7TDMI核采用冯·诺依曼体系结构,使用单-32位总线传送指令和数据,使用三级流水线操作以提高处理器执行速度。ARM7TDMI核可以使用两种指令集:一种是32位ARM指令集;一种是16位Thumb指令集。Thumb指令集是ARM指令集的子集,但它能提供比16位体系结构更高的性能、比32位体系结构更高的代码密度。因此,Thumb指令集使ARM7TDMI核非常适合有存储器宽度和代码密度限制的嵌入式场合。 S3C4510B芯片的存储空间最大可达16M×32bits(包括程序存储区、数据存储区和I/O设备区),它内部集成了一个存储控制器,具有自动刷新存储区数据和自动插入可编程等待周期的功能,可以支持多种类型的存储芯片(包括ROM、SRAM、FLASH和DRAM)。在芯片内部还集成有8K×8bits的指令/数据Cache,采用pseudo-LRU(Least Recently Used)算法,大大提高了芯片的性能。

评论