基于嵌入式系统的实时控制模块设计方案

随着现代通信技术的发展,通信测试仪器不断推陈出新。各种新型设备对系统的实时响应能力的要求越来越高,一种通信测试仪器的实时响应性能,就成为系统设计能否成功的关键因素之一。笔者曾在多个通信测试仪器项目中,成功地应用ARM处理器、C51单片机等为主控芯片的嵌入式系统,实现了对仪器相关模块的实时控制功能。因此提出一种在某通信测试仪器中使用C51单片机来实现实时控制的设计方案。

1 硬件设计与实现

1.1 总体方案设计

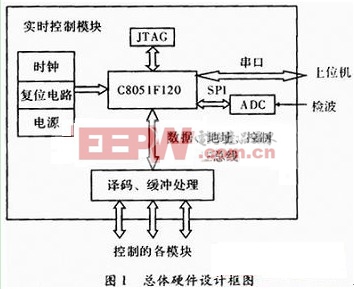

在该通信测试仪器中,实时控制模块主要实现对射频接收频综、射频发生频综、滤波器组件、射频输入模块、射频输出模块等实时控制作用。对射频检波信号进行A/D转换以获取数据。与上位计算机进行通信等功能。

根据待实现的系统功能要求,综合考虑系统资源,及芯片性价比等因素,确定采用以C51单片机为主控芯片的嵌入式系统方案,芯片为Silicon Labs的C8051F120,具有128 kB片内Flash存储器、8×1 024+256 Byte的片内RAM,可寻址64 kB地址空间的外部数据存储器接口、SPI、UART、定时器、时钟振荡器、PLL等,片上外设资源丰富、控制方便。

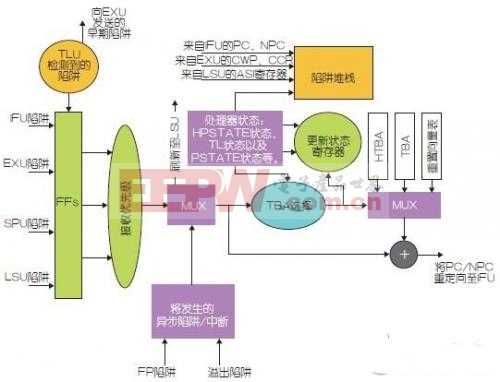

系统资源分配:射频接收、发射频综模块,内含DDS,PLL等,外部控制接口是微控制接口,因此直接用单片机的地址、数据、控制三总线实施控制。滤波组件、射频输入/输出模块等的工作状态与接口上信号电平高低有关,因此用GPIO的方式进行控制。A/D转换控制使用串行外围设备接口SPI.与上位机的通信使用RS-232串口。总体设计框图如图1所示。

1.2 总线及I/O控制的设计

对于射频接收频综、射频发射频综模块,直接采用总线控制,为避免不同的模块控制时相互干扰,用3-8译码器对总线地址译码,产生不同模块的片选信号。同时数据线通过总线收发器以提高带负载能力。对于滤波组件、射频输入/输出等用I/O控制的模块,并未直接使用51芯片的GPIO引脚,则是将数据总线经锁存后模拟GPIO信号供相关模块使用,如图2所示,其中,IO_/WR1由B_/CS7与单片机写线逻辑或后产生。

1.3 SPI及RS232控制接口

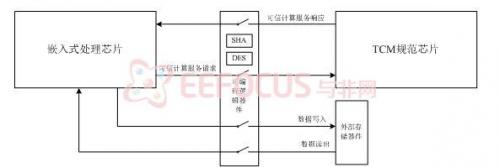

C8051F120芯片上本身自带了A/D转换器,但只有12位,不适合该系统的需求,故在片外另加一片ADI公司的AD7707.其分辨率为16位,是∑-△体系结构,转换的是输入电平的平均值。三通道,输入电平范围可达±10 mV~±10 V.根据实际要求,该系统使用AIN3高电平输入端口,Unbuffered模式,HICOM、REF-接模拟地,VBIAS与REF+均接+2.5 V参考电压,模拟电源5 V,数字电源3.3 V,能检测输入范围为0~10 V的单极性电平。其控制接口是同步串行口,用51芯片的SPI直接控制。图3是AD7707的电气连接图。

评论