新型D/A变换器AD9755及其应用

AD9755是Analog Device公司生产的一种超高速双端数据复用、单路输出的14位数模转换芯片。采用CMOS制造工艺,在单个芯片上集成了高品质14-TxDAC+(r)核、一个基准电压源、兼容TTL数字接口电路单元以及PPL时钟变频器等。它的转换速度很高,可以达到300 Ms/s。

该芯片对外围电路需求少,设计使用灵活方便。AD9755为避免使用复杂、高能耗的ECL电路,而直接利用TTL数字接口来完成300 MHz以下的高性能数摸转换,提供了1条非常便捷的途径。可广泛应用于通信系统信号源、数字信号合成及智能仪器中。其主要特点为:

(1)转换速率300 Ms/s;

(2)垂直分辨率14 B;

(3)工作电压3 V;

(4)无杂散动态范围 SFDR为73 dBc(Fout=50.2 MHz, fDATA=150 MHz条件下);

(5)输入建立时间2.0 ns;

(6)输出建立时间11.0 ns;

1 AD9755的工作原理

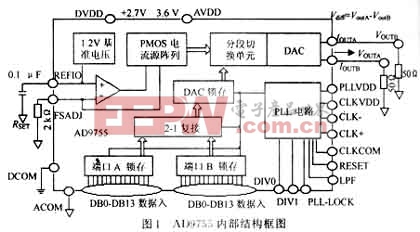

AD9755主要由两组14位数据输入接口、2-1复接器、DAC锁存器、基准电压、PMOS电流源阵列、分段切换器、PLL电路以及DAC单元等构成,其内部结构如图1所示。采用48针LQFP封装形式,图中2个14位兼容TTL电平数据输入端口,每个端口的最大输入频率是150 MHz,2路数据流在片内锁存后,经2-1复接器合成为1路300 MHz并行数据流,再经DAC锁存器锁存后传输到分段切换部件进行处理。

AD9755内置了基准电压源,省去了常规高精度DA转换芯片需要外接基准电压器件的麻烦。图1 中的PMOS电流源阵列是为保证全量程输出电流IOUTFS而特别设计的,IOUTFS的大小由内部的基准控制放大器及外电阻RSET决定。芯片内采用了分段结构,即将数据位分成最高5位,中间4位和最低5位,对各段的数据采用不同的数摸转换方法,以保证数摸转换的精度。分段切换部件将接收到的PMOS电流源阵列输出电流,和经DAC锁存器锁存好的14位数据一起进行相关处理后,输送至末级的DAC部件便实现了整个数模转换过程。

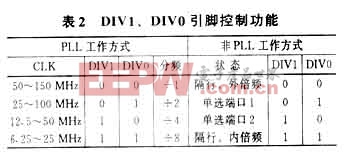

AD9755有使用锁相环(PLL)和不使用锁相环两种工作方式,取决于PLLVDD脚接电源或地。当输入时钟的占空比不是50%时,可使用PLL工作方式。PLL电路内部的VCO可形成100~400 MHz的周期信号,用户通过设定DIV0、DIV1脚来决定该周期信号的分频等级(如表2所示)。PLL在对该分频信号和外部输入时钟进行相位检测后,与锁相环路一起来完成时钟频率的锁定。当不使用锁相环时, DIV0、DIV1脚决定了如表2所示的4种工作状态。在隔行、外倍频方式下,外部时钟应是输入数据率的两倍;在单选1(或2)端口方式(即只完成1路DA变换时),以及在隔行、内倍频方式时外部时钟应设置成与输入数据率相一致。

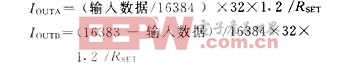

AD9755提供了1对互补电流输出IOUTA,IOUTB,它们都是输入数据的函数,可表示为:

如图1所示,IOUTA,IOUTB,可直接由50 Ω电阻(最好使用有良好温度特性的精密电阻)接到模拟地。最终的差分输出电压值为:(IOUTA-IOUTB)×50。

2 应用设计

下面给出一个以AD9755作为数模转换器来产生任意波形的实例。首先在PC机上进行波形编辑,具体方式可以是表页输入、数学表达式或通过鼠标绘制图形。由软件选择正弦波、通用函数或伪随机噪声等,并设定信号的幅度、频率、偏置量,再经快速演算得到波形数据。波形数据经PCI卡写入到两组大容量SRAM器件(IDT71V3558,最高工作频率200 MHz)后,等待上层系统的DA启动命令。

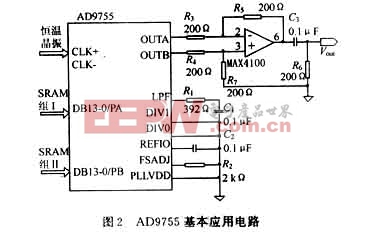

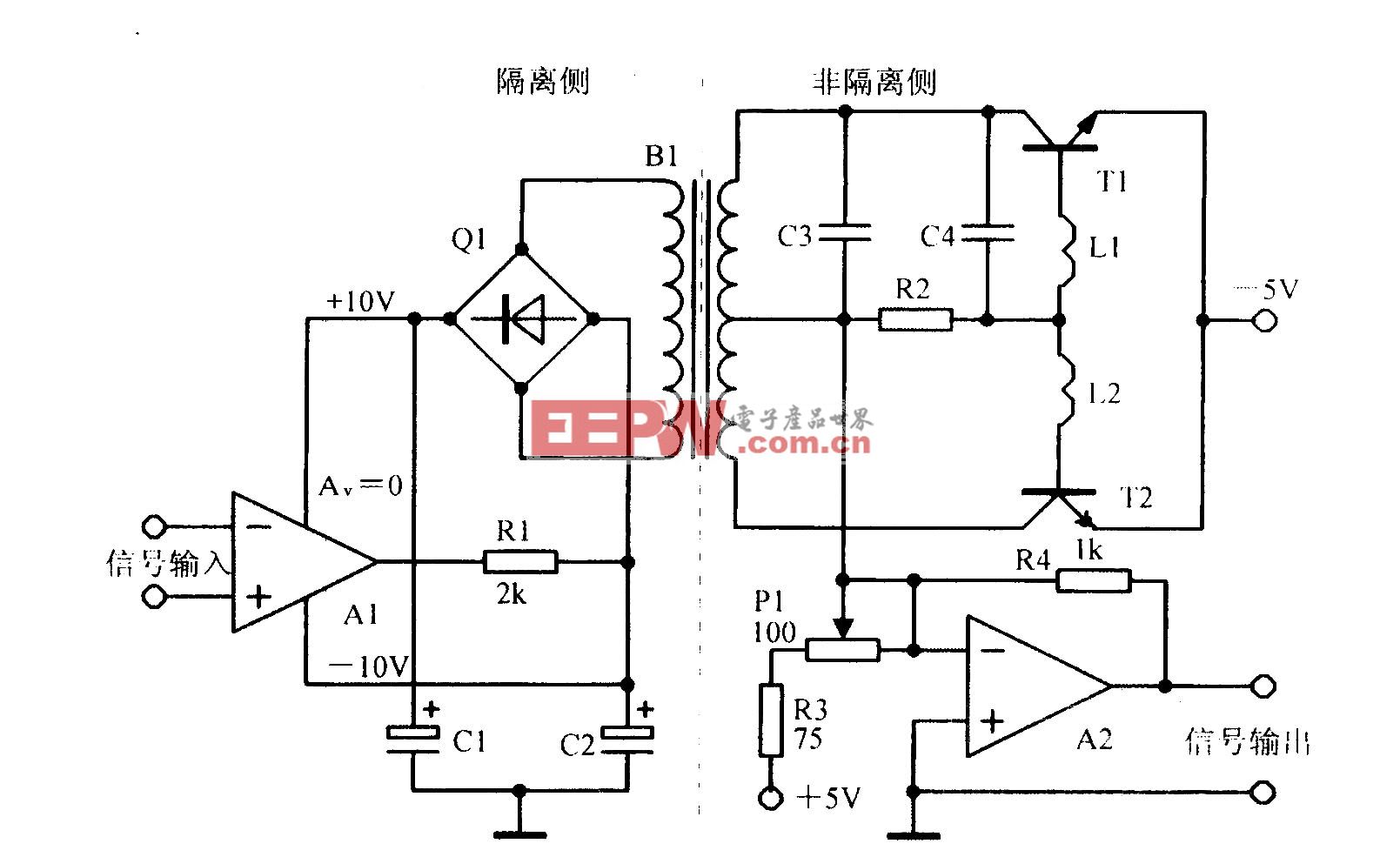

DA启动后,由ISP芯片(isp2128VE,最高工作频率250 MHz)形成75 MHz的高速地址,驱使双路SRAM数据连续并行输出。这两路输出的数据分别输送至AD9755的数据端口1和数据端口2。由于系统采用了高性能的150 MHz恒温晶振,因此AD9755的工作方式简单设定为不使用锁相环的隔行、外倍频方式,应用电路图如图2所示。

值得指出的是,AD9755有着比较灵活的时钟接入方式。可以是差分接入,也可以是单端接入,甚至可以直接使用VP-P在1 V以上的正弦波,不同的接入方式应使用与之相适应的滤波网络。而对于输出信号要求极为严格的应用场合,为了在输出信号上有效抑制杂散电平和消除相位噪声,时钟同步的处理宜选用翻转速度比较好的高性能器件;以保证信号的边沿陡峭、前后抖动最小。

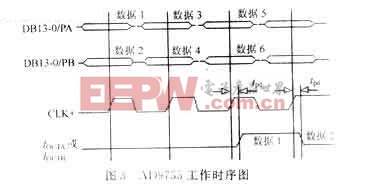

图3给出了AD9755的工作时序图。由于输入数据端口锁存及DAC锁存都发生在CLK的上升沿,为了保证足够的数据建立时间和数据的正确性,两个14位数据端口数据的变化最好在CLK的下降沿完成。DAC的变化时间出现在第3个时钟周期上,并有1个tPD小于1ns的传播延迟。不难看出,AD9755的工作时钟正好是数据变化率的2倍,依次完成了2个数据通道的交替数模转换。SRAM组Ⅰ存放的是任意波形的奇数点数据,而SRAM组Ⅱ存放的是波形的偶数点数据,IOUTA或IOUTB上反映的是与原数据顺序一致的DAC。

由于任意波形的频率成分异常丰富,共模噪声及高次谐波的出现不可避免地会降低输出信号质量。为了改善DA变换的线性度,最大程度地抑制失真与噪声,并提高信号源的负载能力,图2中的输出方法与图1中直接连50Ω到模拟地的方法不同,即引入了宽带运放MAX4100(带宽为500MHz)。

最后需要强调的是,高速TTL数字电路、高速模拟电路,也应和ECL电路要求一样,通过阻抗匹配来克服信号的过冲震荡。按照传输线理论来设计好带线和微带线,PCB连线的阻抗值与电路板铜箔厚度、板层之间填充介质材料及其高度相关,计算办法参见文献2。选用了多层制板,确定电路板层数的根据是:NL=5log[AnfCLK]。其中,An为数据总线宽度,fCLK为最高工作频率。

参考文献

1 AD9755 14-Bit 300MSPS High Speed TxDAC+(r) D/A Converter DatasheetAnalog Devices Inc

2 Martin O′Hara.EMC at Component and PCB. Level.Newnes, 1997.2

基尔霍夫电流相关文章:基尔霍夫电流定律

评论