开关电流电路主要误差的改善的主要方案

1 时钟馈通误差分析

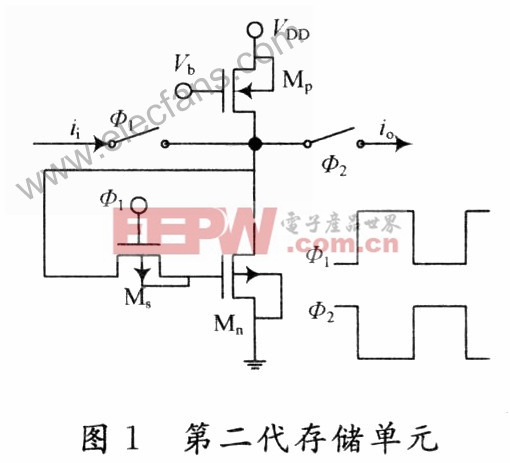

时钟馈通误差是一个复杂的物理现象,在这里以第二代开关电流存储单元为例进行分析。

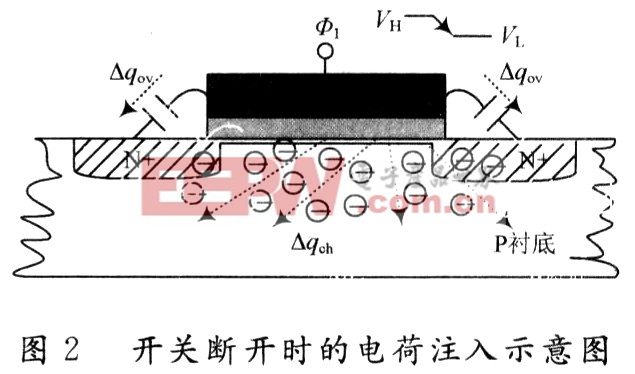

图1为存储单元,图2为开关断开时的电荷注入示意图。

对图1所示的存储单元,Ms的沟道电荷可以近似地描述为:

其中:Cax是栅氧化层单位面积电容;wseff和Lseff分别是Ms的有效沟道宽度和长度;Vgs是Ms的栅一源电压;VT是Ms的阈值电压,由式(2)给出:

式中:2 |φF|是强反型层表面势垒;r是体阈值参数;VT0是Vgs=0时的阈值电压。

一般情况下,1 V

将式(3)代入式(1),得到注入存储电容的沟道电荷为:

其中:aq表示沟道电荷注入存储电容的分配系数,典型值为:aq=1/2。由栅极扩散覆盖电容Co1,注入存储电容的电荷为:

根据式(4)和式(5)司得整个注入电荷的总量为:

式中:mi=ii/j,称为调制指数。将式(9)代入式(8),得:

2 传输误差分析

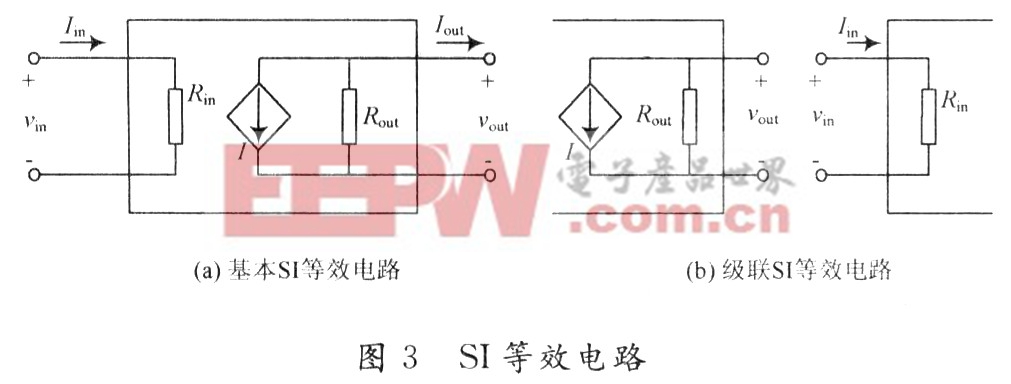

开关电流电路属于电流模式电路,其基本结构的等效电路如图3所示。

从图3可以看出,上一级电路的输出电阻与下一级电路的输入电阻并联。设上一级电路的输出电流为Iout,输出电阻为Rout,下一级电路的输入电流为Iin,输入电阻为Rin。,则下一级电路的输入电流为:

从式(12)可看出,增大输出电阻或减小输入电阻都可以减小传输误差。

3 误差的改善方法

(1)时钟馈通误差的改善。改善时钟馈通误差可采用S2I电路。图4给出S2I存储单元的电路和时序。它的工作原理为:在φ1a相,Mf的栅极与基准电压Vref相连,此时Mf为Mc提供偏置电流JoMc中存储的电流为ic=J+ii。当φ1a由高电平跳变为低电平时,由于时钟馈通效应等因素造成Mc单元存储的电流中含有一个电流误差值,假设它为△ii。,则Mc中存储的电流为ic=J+ii+△ii。在φ1b相期间,细存储管Mf对误差电流进行取样,由于输入电流仍然保持着输入状态,所以Mf中存储的电流为If=J+△ii。当φ1b由高电平跳变为低电平时,考虑到△ii。

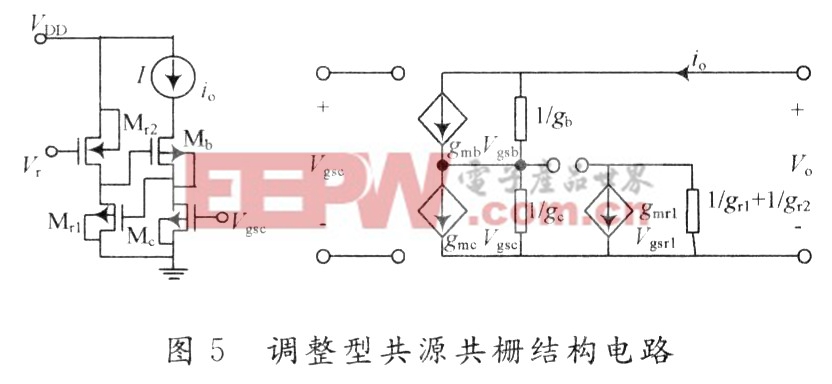

(2)传输误差的改善。从前面的分析知,增大输出电阻或减小输入电阻都可以减小传输误差。下面介绍一种调整型共源共栅结构电路,见图5。

由图5可计算出输出电阻为:

与图1中第二代基本存储单元相比,输出电阻增大

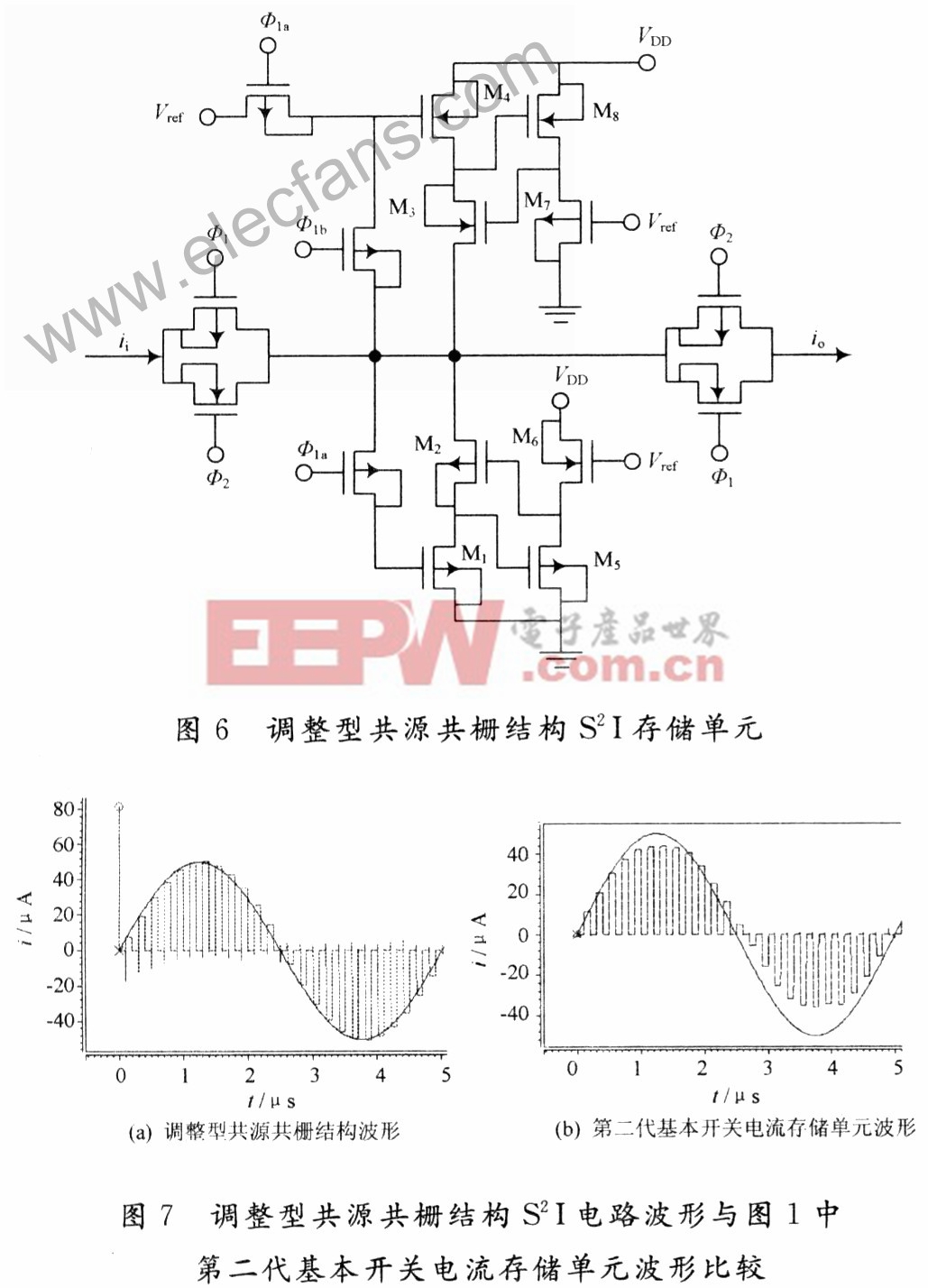

结合S2I电路与调整型共源共栅结构电路的优点,构造调整型共源共栅结构s2I存储单元,见图6。

4 仿真及结果

采用0.5 pm标准数字CMOS工艺对图6电路仿真,仿真参数如表1所示:

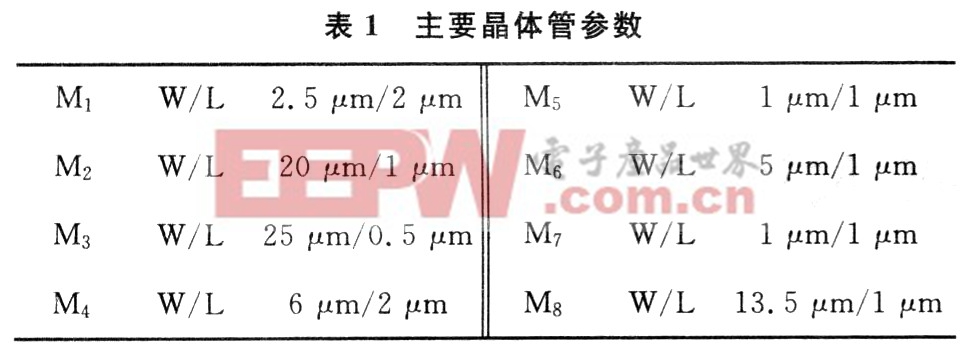

所有NMOS衬底接地,所有PMOS衬底接电源。所有开关管宽长比均为0.5/μm/0.5 μm。输入信号为振幅50μA,频率200 kHz的正弦信号,时钟频率5 MHz,V ref一2.4 V,VDD=5 V。表1中给出了主要晶体管仿真参数。HSpice仿真结果见图7(a)。对图1中第二代基本存储单元仿真结果见图7(b)。

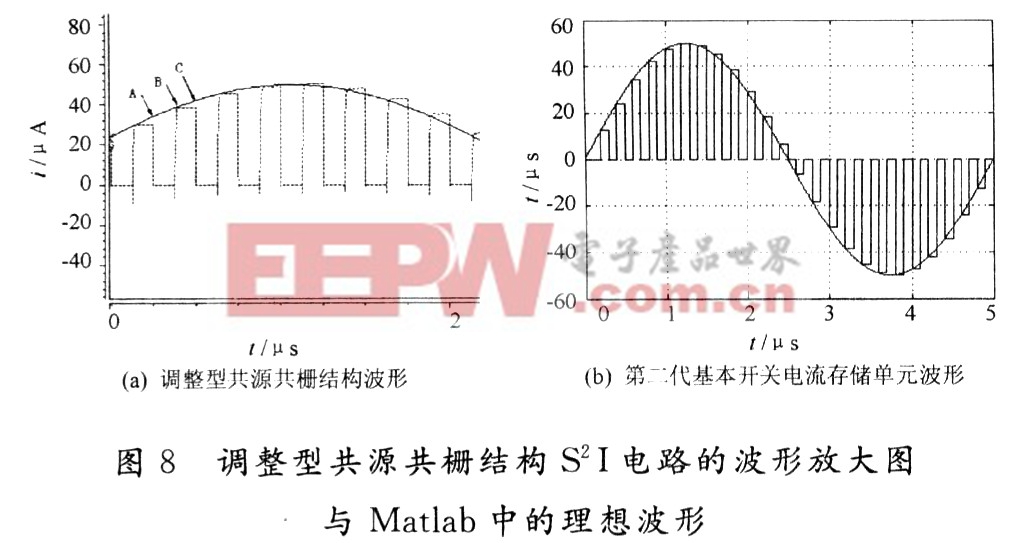

从图7中可以看出,调整型共源共栅结构S2I电路大大提高了精度。图8(a)是图7的放大图,图8(b)是Matlab中的理想波形。从图8(a)可以看出,在A点时,输出开关断开,输入开关闭合,输出电流变为零。在AB区间内,输入信号对存储管的寄生电容充电。在B点,输出开关闭合,输入开关断开,输出电流为B点的电流值,半个时钟周期后,在C点,输出开关断开,输入开关闭合,继续重复上一周期对输入电流的采样一保持。整个电路全由MOS管构成,依靠晶体管的栅极寄生电容对输入信号采样一保持,所以可以与标准数字CMOS工艺兼容,与数字电路集成在1块芯片上。与Matlab中的理想波形对比后可以看出此电路的性能相当精确。

5 结 语

与开关电容电路相比,开关电流电路不需要线性浮置电容,能够与标准数字CMOS工艺兼容。但是由于误差的存在,至今无法完全取代开关电容电路。这里分析了开关电流电路中的时钟馈通误差与传输误差,并提出了解决办法,从仿真结果可以看出改进后的电路性能大大提高,精确完成了对输人信号的采样一保持。

评论